W&T Wetenschap & Technologie

Een plek om te discussiëren over wetenschappelijke onderwerpen, wetenschappelijke problemen, technologische projecten en grootse uitvindingen.

Waarom stellen de internetmedia geen redacteur aan die het taalgebruik eens grondig corrigeert?

De component, om preciezer te zijn: mannelijk.

De component, om preciezer te zijn: mannelijk.

Onderschat nooit de kracht van domme mensen in grote groepen!

Der Irrsinn ist bei Einzelnen etwas Seltenes - aber bei Gruppen, Parteien, Völkern, Zeiten die Regel. (Friedrich Nietzsche)

Der Irrsinn ist bei Einzelnen etwas Seltenes - aber bei Gruppen, Parteien, Völkern, Zeiten die Regel. (Friedrich Nietzsche)

Tweakersquote:Micron brengt phase change-geheugen voor mobiele apparaten uit

Micron heeft de eerste chips met phase change-geheugen voor grootschalige afname beschikbaar gemaakt. De geheugenfabrikant gaat producten leveren waarin een phase change-geheugen met een 1Gb-chip zit, gecombineerd met 512Mb ddr2.

De nieuwe geheugenchips, of correcter: packages met de pcm-chips en lpddr2-chips erin, zullen aan fabrikanten van mobiele apparatuur als laptops, tablets en mobiele telefoons geleverd worden. De packages zouden vooral geoptimaliseerd zijn voor zogeheten feature phones, later zouden geavanceerdere toestellen als smartphones en tablets volgen. Volgens Micron biedt de beschikbaarheid van de packages fabrikanten van chipsets en mobieltjes de gelegenheid hun producten te optimaliseren om van de voordelen van phase change-geheugen te profiteren.

Phase change-geheugen zou een stuk zuiniger zijn dan conventioneel geheugen en bovendien een langere levensduur hebben. Apparaten zouden onder meer sneller starten met Microns pcm-chips aan boord. Het phase change-geheugen dat door Micron ontwikkeld werd, wordt op 45nm geproduceerd. Het werkt niet zoals conventioneel geheugen door lading in condensators vast te houden en zo bits op te slaan. In pcm is het verschil in weerstand tussen een kristallijne vorm en een amorfe toestand van een speciaal materiaal verantwoordelijk voor de enen en nullen. Het geheugentype ontleent zijn naam aan de overgang tussen de twee toestanden, de phase change.

Dit geheugen wordt ook vaak als reram omschreven. Een goede ontwikkeling deze typen geheugen zijn als flashcache heel erg geschikt omdat het snel is en vooral het aantal directe schrijfacties naar flashram verminderd. Dit alles maakt de snelheid veel hoger en de levenduur veel langer.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

synaptic-electronic-circuits-that-learn-and-forget-like-neural-processesquote:Synaptic electronic circuits that learn and forget like neural processes

mana_synaptic_electronics

(a): Volatile (short-term) memory property of two terminal device before the forming process. Current change observed by applying sequence of positive voltage pulses at intervals of 40 s and widths of 0.5 s. (b): Nonvolatile (long-term) memory property in the device after the forming process following application of a sequence of positive and negative pulses with widths of 0.1 ms. (c): Schematic illustration of the device structures before and after forming process. (Credit: MANA, NIMS)

Rui Yang, Kazuya Terabe and colleagues at the National Institute for Materials Science (NIMS), and the International Center for Materials Nanoarchitectonics (MANA) in Japan and at the California NanoSystems Institute/UCLA have developed “nanoionic” (processes connected with fast ion transport in all-solid-state nanoscale systems) devices capable of a broad range of neuromorphic and electrical functions.

Background

Such a device would allow for fabrication of on-demand configurable circuits, analog memories, and digital-neural fused networks in a single device architecture.

Synaptic devices that mimic the learning and memory processes in living organisms are attracting interest as an alternative to standard computing elements to help extend performance beyond current physical limits. However, artificial synaptic systems have been hampered by complex fabrication requirements and limitations in the learning and memory functions they mimic.

How it works

The device is based on a platinum-tungsten trioxide (WO3–x) device using oxygen ions migrating in response to voltage sweeps. Accumulation of the oxygen ions at the electrode leads to Schottky diode-like potential barriers and resulting changes in resistance and rectifying characteristics. The stable bipolar switching behavior at the platinum-tungsten trioxide-based device is attributed to the formation of a conductive filament and oxygen absorbability of the platinum electrode.

The researchers noted that the device properties* — volatile and non-volatile states and current fading following positive voltage pulses — are similar to neural behavior — that is, short- and long-term memory and forgetting processes.

The device was found to possess a wide range of time scales of memorization, resistance switching, and rectification varying from volatile to permanent in a single device.

“These capabilities open a new avenue for circuits, analog memories, and artificially fused digital neural networks using on-demand programming by input pulse polarity, magnitude, and repetition history,” the researchers conclude.

* In its initial pristine condition the system has very high resistance values. Sweeping both negative and positive voltages across the system decreases this resistance nonlinearly, but it soon returns to its original state, indicating a volatile state. Applying either positive or negative pulses at the top electrode introduces a soft breakdown, after which sweeping both negative and positive voltages leads to non-volatile states that exhibit bipolar resistance and rectification for longer periods of time.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:The neuristor HP-labs

The Hodgkin–Huxley model for action potential generation in biological axons1 is central for understanding the computational capability of the nervous system and emulating its functionality. Owing to the historical success of silicon complementary metal-oxide-semiconductors, spike-based computing is primarily confined to software simulations2, 3, 4 and specialized analogue metal–oxide–semiconductor field-effect transistor circuits5, 6, 7, 8. However, there is interest in constructing physical systems that emulate biological functionality more directly, with the goal of improving efficiency and scale. The neuristor9 was proposed as an electronic device with properties similar to the Hodgkin–Huxley axon, but previous implementations were not scalable10, 11, 12, 13. Here we demonstrate a neuristor built using two nanoscale Mott memristors, dynamical devices that exhibit transient memory and negative differential resistance arising from an insulating-to-conducting phase transition driven by Joule heating. This neuristor exhibits the important neural functions of all-or-nothing spiking with signal gain and diverse periodic spiking, using materials and structures that are amenable to extremely high-density integration with or without silicon transistors.

Nature

Het gaat nu snel met de ontwikkeling van geavanceerde AI neuronen. Technologische singulariteit ga ik nog meemaken als ik gezond blijf

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Tja, het is allemaal nogal complex, waar het op neer komt is dat men de functies van neuronen (hersencellen) steeds beter kan nabootsen middels memristors. Dat is ook niet zo verwonderlijk aangezien neuronen analoog-digitaal hybride zijn. Dat wil zeggen dat ze een analoge en digitale functie combineren. De huidige digitale techniek overtreft al verre die van biologische systemen qua snelheid en betrouwbaarheid. Echter analoog was er een aanzienlijk manko. AD-DA converters vreten stroom en er zijn nogal wat transistors nodig voor voor slechts 1 analoog kanaal. De nieuwe schakelingen zoals bijv de neuristor laten zien dat biologische neuronen in (bijna) alle opzichten overtroffen zullen worden.quote:

De volgende horde is het energieverbruik, menselijke hersenen zijn ongelovelijk efficient vergeleken met de huidige elektronica.

[ Bericht 0% gewijzigd door Digi2 op 27-12-2012 17:34:27 ]

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:Onderzoeker wil memristors gebruiken voor neurale netwerken

Een Duitse onderzoeker wil een kunstmatig brein bouwen met memristors als belangrijkste bouwstenen. Dergelijke neurale netwerken zouden tot leren in staat moeten zijn. De wetenschapper wil een blauwdruk voor de bouw van kunstmatige hersenen ontwikkelen.

De Duitse onderzoeker Andy Thomas is docent aan de natuurkundefaculteit van de universiteit van Bielefield en publiceert zijn plannen voor een blauwdruk in maart in het Journal of Physics. Uitgangspunt voor de bouw van een neuraal netwerk dat tot leren in staat is, moet het gebruik van memristors zijn. Die relatief recent ontdekte elektronische bouwstenen zijn passieve elementen, net als weerstanden. Anders dan weerstanden behoudt een memristor echter zijn laatste weerstand wanneer het circuit onderbroken wordt. Aan dat geheugengedrag dankt de memristor zijn naam.

Bovendien zou een 'geheugenweerstand' die zijn laatste weerstand onthoudt, het elektronische equivalent van een synaps zijn. In hersenen zorgen synapsen voor de onderlinge verbindingen tussen neuronen. Omdat memristors in functie op synapsen lijken, wil Thomas ze inzetten als bouwstenen voor zelflerende neurale netwerken. Hun geschiktheid werd al eerder aangetoond door Thomas' eigen onderzoeksgroep en door andere onderzoekers, onder meer van Intel.

Omdat de weerstand van een memristor afhankelijk is van de stroom die er doorheen gaat, is veel meer variatie mogelijk dan bij bits; die kunnen immers alleen een 1 of een 0 representeren. Memristors fungeren meer analoog, zoals samenwerkende synapsen in hersenen dat ook doen. Bovendien zou een neuraal netwerk met memristors niet alleen in staat zijn tot leren, maar ook tot vergeten. Een dergelijk neuraal netwerk is in theorie ook te bouwen met conventionele, op transistors gebaseerde circuits, maar gebruik van passieve componenten als memristors, met hun aan synapsen analoge functie, maakt dat een stuk eenvoudiger.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Bronquote:Resistive RAM – A New Approach

Resistive random-access memory (RRAM) is widely hailed as the “most likely to succeed” in the race to develop a new more scalable, high capacity, high performance and reliable memory.

Typical RRAM cells are based on a switching material with different resistance characteristics sandwiched by two metallic electrodes. The switching effect of RRAM is based on the motion of ions under the influence of an electric field or heat, and the ability of the switching material to store the ion distribution, which in turn causes a measurable change of the device resistance.

Compared to traditional Flash memory, RRAM is faster, bit-alterable and requires lower voltage, enabling its use in both embedded and SSD applications. The simple RRAM cell structure offers best area efficiency (4F2 cell) and excellent scalability and 3D integration potential (both 3D stacking and vertical cell). RRAM requires lower programming currents than PCM or MRAM with comparable performance in terms of retention and endurance.

There are different approaches to implementing RRAM, based on different switching materials and memory cell organization. Those variables drive significant performance among the different materials being used.

RRAM has already been the subject of intense research and development, with several companies claiming to have prototype memory chips available in the next 1-2 years.

One of the biggest challenges for RRAM technology has been the integration of the RRAM array with standard CMOS technology and standard manufacturing processes. Crossbar RRAM technology has proven the manufacturability with a working array produced in a commercial fab. This working silicon is a fully integrated monolithic CMOS controller and memory array chip. The company is currently completing the characterization and optimization of this device and plans to bring its first product to market in the embedded SOC market.

Een nieuw bedrijf is verschenen dat memristor geheugen wil gaan produceren en verkopen. Hopelijk zet dit Hynix/Hp en Samsung aan hun eigen memristor geheugen op de markt te introduceren. Samsung en Hynix lijken geen haast te maken mogelijk omdat ze eerst de flashmarkt willen uitmelken. Dit nieuwe bedrijf produceert zelf geen flash en heeft memristor geheugen als core business. Hopelijk volgt nu een race naar een snelle markt introductie.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Kan beter het jaar van de Resistor wordenquote:Op vrijdag 24 januari 2014 23:50 schreef Senor__Chang het volgende:

Kick!

Nog nieuws omtrent de Memristor? Dit jaar zou het jaar van deze component moeten worden.

Maar ik verwacht meer doorbraken op het gebied van quantum computing, is afgelopen jaar een beetje ondergesnowdend.

Als het niet met een hamer te repareren is, is het een elektrisch probleem.

Of van grafeen, of phosphorenequote:Op zaterdag 25 januari 2014 00:19 schreef Resistor het volgende:

[..]

Kan beter het jaar van de Resistor worden

Maar ik verwacht meer doorbraken op het gebied van quantum computing, is afgelopen jaar een beetje ondergesnowdend.

Gaan we eindelijk weer een groei in de kloksnelheid zien? Ik lees vaak berichten over een doorbraak, maar altijd valt dat wel mee. Nu vraag ik me af of er onder die sensatieberichten wel een gestage stijgende lijn is te vinden in deze technologie(en).

Het zal wel groot nieuws worden als die dingen toegepast gaan worden. Wanneer weten 'wij' als geïnteresseerde consument niet.

Verder is er nog http://www.memristor.org/ , makkelijke bron met informatie over dit onderwerp. (en nieuws, valt tegen dat deze site nog niet genoemd is)

En ligt het aan mij, of zijn er meer mensen die hoofdpijn krijgen van het icon van Digi2, als ik er te lang naar kijken willen mijn ogen zich scherp stellen, maar dat lukt niet.

Verder is er nog http://www.memristor.org/ , makkelijke bron met informatie over dit onderwerp. (en nieuws, valt tegen dat deze site nog niet genoemd is)

En ligt het aan mij, of zijn er meer mensen die hoofdpijn krijgen van het icon van Digi2, als ik er te lang naar kijken willen mijn ogen zich scherp stellen, maar dat lukt niet.

Als het niet met een hamer te repareren is, is het een elektrisch probleem.

quote:ARM investeert in ceram-geheugentechnologie

Door Dimitri Reijerman

ARM heeft geld gestoken in Symetrix, een bedrijf dat onderzoek doet naar correlated-electron ram, een relatief nieuw type niet-vluchtig geheugen. Ceram zou verder verkleind kunnen worden dan de huidige soorten flashgeheugen.

CeramCeram kan volgens Symetrix een goede opvolger zijn van de huidige nand-flashgeheugentechnologie die niet verder verkleind zou kunnen worden dan tot een 20nm-procedé. De Ceram-technologie, een verbeterd ontwerp ten opzichte van het moeilijk te fabriceren reram, zou schaalbaar zijn tot 5nm, zo stellen de makers. Ook zou de ceram-geheugentechnologie in socs geïntegreerd kunnen worden.

ARM heeft interesse in de ceram-technologie en heeft volgens de website Electronics360 besloten om geld te investeren in Symetrix. Onduidelijk is nog hoe hoog het bedrag is, maar ARM zou belangstelling hebben om de technologie op termijn mogelijk in licentie te nemen.

Tot nu toe heeft ARM zich vooral gericht op processortechnologie. Het bedrijf geeft zijn chipontwerpen in licentie uit aan fabrikanten. ARM-chips zijn vooral populair in mobieltjes en tablets dankzij het relatief geringe stroomverbruik.

quote:Non-Filamentary ReRAM

Carlos Paz de Araujo, a professor at the University of Colorado and an expert in ferroelectric memory and materials, has revealed that his company Symetrix Corp. is preparing to launch a non-filamentary, non-volatile memory technology based on the metal-insulator Mott transition in nickel oxide.

The development was revealed on the web pages of EE Times in an online forum discussing non-volatile memory in which Professor Araujo said he was "sick and tired of these electrochemical approaches claiming to solve all problems when in fact the beauty of metal-insulator physics is not utilized."

There have been numerous R&D initiatives to try and develop a resistive RAM (ReRAM) replacement for flash memory, but most of these are based on the making and breaking of conductive filaments within an insulating sandwich between electrodes. Understanding and controlling the physical processes behind the forming, maintenance, and breaking of such filaments, which can be just one or a few atoms in diameter, has proved difficult.

Professor Araujo claimed his approach is different in that it is non-filamentary and does not depend on mass transport. Instead it uses a metal-insulator transition that occurs throughout the metal-oxide crystal structure and that is dependent on electron correlation. The metal-insulator transition is controlled by doping, with nickel carbonyl as the dopant, Professor Araujo said in his comments.

"We call our device CeRAM -- Correlated Electron RAM -- to separate ourselves from the filament crowd," Professor Araujo wrote on the EE Times website.

"We are introducing this technology in two months. It is fully compatible with lithography down to 20nm and can go lower. It is free of complicated contact materials such as platinum. It uses aluminum, cobalt silicide and nickel silicide. Anneals at 400 degrees C and is integratable in 3D using the same electrodes with an already proven diode. The storage temperature is 400 degrees C and the read/write is in the picoseconds. Blue Sky? Not really, it is common sense to try to dope nickel oxide instead of breaking it with filaments," Professor Araujo wrote.

Professor Araujo added that the technology reads at 0.2 volts, writes at 0.6 and 1.2 volts, and has a read endurance above 10^13 cycles, which is far in excess of the numbers quoted for flash memory at the leading-edge and for most alternative ReRAM technologies.

The end of scaling for the mainstream non-volatile memory technology, flash memory, which is based on electron storage, has been predicted for many years. Flash memory has just started to be implemented in multiple layers at relaxed minimum geometries to try and circumvent this issue. (See Samsung Confirms 24 Layers in 3D NAND.)

ReRAM memory, often based on layered metal-oxide materials, including transition metals, has yet to enter high-volume production and phase-change memory (PCM) although commercially deployed is only made at a lower storage density and features sizes much larger than flash memory.

Symetrix, based in Colorado Springs, Colo., was formed in 1986 by Professor Araujo to work on ferroelectric materials for use in non-volatile memory. Symetrix advocated the use of strontium barium titanate (SBT) as an alternative perovskite to lead zirconate titanate (PZT) for use in non-volatile ferroelectric random access memories (FeRAMs). Symetrix, which operates an IP-licensing business model, has licensed its technology to a number of semiconductor companies.

"We do not follow the capital-raising path and we are 27 years old with a portfolio of over 200 patents. We sold many licenses, and the royalty stream is enough to continue innovation," Professor Araujo wrote, but added that the company might be open to equity investment to accelerate the development of CeRAM.

EE Times wrote to Professor Araujo with supplementary questions about the nickel-oxide memory technology, but he declined to provide further information for publication at this time.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Buiten de labs is nog weinig van de memristor technologie te zien. Alleen Panasonic past het kleinschalig toe in commerciele produkten.quote:

HP claimt smartphones met 100 terabyte opslag

HP heeft een nieuwe computerarchitectuur gepresenteerd die zuiniger en zes keer sneller is dan de huidige servers en in staat is smartphones 100 terabyte opslagruimte te geven.

HP claimt smartphones met 100 terabyte opslag.

HP heeft zijn nieuwe architectuur de naam The Machine gegeven, en noemt het een van de grootste doorbraken op computergebied in decennia.

In eerste instantie is de nieuwe computerarchitectuur ontworpen om beter om te kunnen gaan met de grote datastroom van het zogenoemde Internet of Things. Dat is een verzamelnaam voor het groeiend aantal huishoudelijke en consumentenapparaten met (zelfstandige) internettoegang.

Zo heeft The Machine niet enkele krachtige processorkernen, maar clusters van vele kleinere processoren die specifieke taken uitvoeren. Alles is verbonden met fotonica: optische gegevensoverdracht die veel sneller moet zijn dan de huidige koperen kabels. Ionen worden daarbij in plaats van elektronen gebruikt voor het maken van berekeningen.

Razendsnel geheugen

Ook bevat The Machine zogenoemde memristors; de opvolger van de transistor die niet alleen gebruikt kan worden voor rekentaken, maar ook voor opslag. Dat maakt dat het permanente geheugen van The Machine zo snel is als werkgeheugen. Door die twee stappen in het computerproces te combineren, zijn bovendien kleinere, zuinigere apparaten met meer opslagruimte mogelijk.

The Machine kan volgens HP 160 petabyte (160 miljoen gigabyte) aan data in 250 nanoseconden behandelen. Dat is zes keer sneller dan huidige serverhardware, toch verbruikt The Machine daarbij 80 procent minder energie.

Geen koper

Omdat de architectuur van The Machine geen koper gebruikt, maar fotonica, zijn andere vormen van computers mogelijk. Daarom denkt HP dat het de technologie ook kan laten krimpen voor gebruik in laptops en smartphones.

"Vandaag de dag wisselen al onze apparaten, van telefoon tot supercomputer, constant informatie uit tussen drie lagen van geheugen", legt HP uit. "We hebben het SRAM voor informatie die nu nodig is, het DRAM voor informatie die spoedig nodig is, en het opslaggeugen voor data die later nodig is. Memristors zullen een snelle, goedkope manier zijn die DRAM en opslag combineert. Door het elimineren van een stap maken we processen sneller en zuiniger. Denk aan 100 terabyte opslag in je mobiele telefoon."

Het gaat dan met name om die memristors, die meer en snellere opslag in een kleinere verpakking mogelijk maken. Dit geheugen is pas volgend jaar in testhoeveelheden verkrijgbaar. De eerste apparaten die gebruik maken van de techniek van The Machine worden in 2018 verwacht.

Toch benadrukt HP dat The Machine nog een onderzoeksproject is, wat het onduidelijk maakt of en wanneer de technologie daadwerkelijk te gebruiken is

Mouser to ship Panasonic's latest ReRAM-based MCUs

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

waarom komt het niet op de grote markt? te duur?

Trots lid van het 👿 Duivelse Viertal 👿

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Ik zie even niet waarom 100 TB opslag nou interessant zou zijn voor smartphones, of wat dat uberhaupt met smartphones te maken heeft.

Desalniettemin interessante ontwikkelingen!

Desalniettemin interessante ontwikkelingen!

Niet meer aanwezig in dit forum.

als je 100 TB in een telefoon kan stoppen zou je het ook in een digitale filmcamera kunnen stoppen en niet gecomprimeerde beelden opslaan op de hoogste resolutie.quote:Op donderdag 12 juni 2014 09:38 schreef Molurus het volgende:

Ik zie even niet waarom 100 TB opslag nou interessant zou zijn voor smartphones, of wat dat uberhaupt met smartphones te maken heeft.

Desalniettemin interessante ontwikkelingen!

Aan de andere kant als met deze technologie een smartphone ongeveer even krachtig of krachtiger wordt dan huidige desktops wil je misschien ook wat extra opslagruimte.

ik wil wel de complete piratenbaai op mijn smartphone!

Trots lid van het 👿 Duivelse Viertal 👿

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Ik weet niet hoe makkelijk het is om x86 compatibel hardware te maken met deze technologiequote:Op donderdag 12 juni 2014 08:51 schreef Maanvis het volgende:

waarom komt het niet op de grote markt? te duur?

aan de andere kan als de nieuwe hardware maar krachtig genoeg is kan je alle oude software via virtual machines draaien

het zal wel als eerste in HPC systemen gebruikt gaan worden.. daarna pas betaalbaar voor high-end servers (zoals Itanium was) en daarna pas home desktop. maar de x64 standaard is nu wel zoooo standaard geworden.. dat ik me idd afvraag hoelang het gaat duren voor dit gemeengoed is

Any previously enabled store events for this user, including notifications to other users, may fail to fire

Zodra de hardware krachtig en goedkoop genoeg is kan het snel gaan als er maar goede emulatie voor de oude windows/mac/linux versies aanwezig is.quote:Op donderdag 12 juni 2014 11:09 schreef Parzival het volgende:

het zal wel als eerste in HPC systemen gebruikt gaan worden.. daarna pas betaalbaar voor high-end servers (zoals Itanium was) en daarna pas home desktop. maar de x64 standaard is nu wel zoooo standaard geworden.. dat ik me idd afvraag hoelang het gaat duren voor dit gemeengoed is

Heb je wel enig idee hoeveel 100 TB is? Daarmee kun je bijna een leven lang non-stop filmen. Nu overdrijf ik misschien een beetje, maar het zit er niet ver naast.quote:Op donderdag 12 juni 2014 10:59 schreef Mr.44 het volgende:

[..]

als je 100 TB in een telefoon kan stoppen zou je het ook in een digitale filmcamera kunnen stoppen en niet gecomprimeerde beelden opslaan op de hoogste resolutie.

Aan de andere kant als met deze technologie een smartphone ongeveer even krachtig of krachtiger wordt dan huidige desktops wil je misschien ook wat extra opslagruimte.

Niet meer aanwezig in dit forum.

ongecomprimeerde data voor een 1080p 24 fps film is 667 GB/uurquote:Op donderdag 12 juni 2014 11:32 schreef Molurus het volgende:

[..]

Heb je wel enig idee hoeveel 100 TB is? Daarmee kun je bijna een leven lang non-stop filmen. Nu overdrijf ik misschien een beetje, maar het zit er niet ver naast.

De Hobit is geschoten is 48 fps dus dat is al meer dan een TB voor ieder uur

en in 4k dus dan ga je van 2 megapixels naar 8,8 megapixels

een uur of 17 ruwe film moet je wel kwijt kunnen

17 uur op die resolutie filmen met je mobiele telefoon is natuurlijk nog steeds absurd.quote:Op donderdag 12 juni 2014 12:51 schreef Mr.44 het volgende:

[..]

ongecomprimeerde data voor een 1080p 24 fps film is 667 GB/uur

De Hobit is geschoten is 48 fps dus dat is al meer dan een TB voor ieder uur

en in 4k dus dan ga je van 2 megapixels naar 8,8 megapixels

een uur of 17 ruwe film moet je wel kwijt kunnen

Ik zou die 100 TB veel liever in m'n NAS drive hebben zitten dan op mijn telefoon. Mooie ontwikkeling... maar wat dit nu met telefoons te maken heeft is mij een volslagen raadsel.

Niet meer aanwezig in dit forum.

Merkwaardige tekst, met opmerkelijke fouten. Ik vraag af of de journalist we begreep waar hij het over had en of zijn nieuws dus wel betrouwbaar is.quote:Op donderdag 12 juni 2014 07:53 schreef Digi2 het volgende:

[..]

Buiten de labs is nog weinig van de memristor technologie te zien. Alleen Panasonic past het kleinschalig toe in commerciele produkten.

Mouser to ship Panasonic's latest ReRAM-based MCUs

Onderschat nooit de kracht van domme mensen in grote groepen!

Der Irrsinn ist bei Einzelnen etwas Seltenes - aber bei Gruppen, Parteien, Völkern, Zeiten die Regel. (Friedrich Nietzsche)

Der Irrsinn ist bei Einzelnen etwas Seltenes - aber bei Gruppen, Parteien, Völkern, Zeiten die Regel. (Friedrich Nietzsche)

Er zit wel een klein verschil tussen 17 uur en 'Daarmee kun je bijna een leven lang non-stop filmen. Nu overdrijf ik misschien een beetje, maar het zit er niet ver naast.'.quote:Op donderdag 12 juni 2014 12:59 schreef Molurus het volgende:

[..]

17 uur op die resolutie filmen met je mobiele telefoon is natuurlijk nog steeds absurd.

Ik zou die 100 TB veel liever in m'n NAS drive hebben zitten dan op mijn telefoon. Mooie ontwikkeling... maar wat dit nu met telefoons te maken heeft is mij een volslagen raadsel.

Hoeveel uur film heb jij dan al opgenomen met je telefoon?quote:Op maandag 16 juni 2014 10:23 schreef heegenees het volgende:

[..]

Er zit wel een klein verschil tussen 17 uur en 'Daarmee kun je bijna een leven lang non-stop filmen. Nu overdrijf ik misschien een beetje, maar het zit er niet ver naast.'.

Voor een gewone gebruiker is 17 uur op een leven veel denk ik.

En doe je dat op de nu voor telefoons gangbare resoluties dan red je 'een leven lang non-stop' ook nog wel denk ik. Want we praten wel over 17 uur bioscoop kwaliteit ongecomprimeerd.

Niet meer aanwezig in dit forum.

Een filmpje op mijn telefoon van 57 seconde is 116 Mb.quote:Op maandag 16 juni 2014 10:51 schreef Molurus het volgende:

[..]

Hoeveel uur film heb jij dan al opgenomen met je telefoon?

Voor een gewone gebruiker is 17 uur op een leven veel denk ik.

En doe je dat op de nu voor telefoons gangbare resoluties dan red je 'een leven lang non-stop' ook nog wel denk ik. Want we praten wel over 17 uur bioscoop kwaliteit ongecomprimeerd.

Dat betekend dat het ongeveer 2 Mb per seconde is.

100 TB = 100 x 1024 = 102.400 Gb

102.400 x 1024 = 104.857.600 MB

104.857.600 / 2 = 52.428.800 seconde filmen

52.428.800 / 3600 (uren) = 14.563.5 uur

14.563.5 uur / 24 = 606 en ongeveer 20 uur

Vrij veel inderdaad, ik zal het niet snel volschieten

Het verwondert mij dat niemand hier al gezegd heeft dat wat HP een memristor noemt (en alle andere ReRAM cellen, CBRAM en soortgelijken) eingenlijk niets te maken heeft met het vierde fundamentele device (de memristor van de startpost):

Het vierde fundamenteel component moet de koppeling leggen tussen magnetische flux en elektrische lading, maar voor zover ik weet is dit nog altijd niet gevonden...

ReRAM heeft nu helaas nog meer dan voldoende problemen: moeilijk goedkoper te maken dan NAND flashgeheugen, hoge schrijfstroom, variabiliteit, ...

Het vierde fundamenteel component moet de koppeling leggen tussen magnetische flux en elektrische lading, maar voor zover ik weet is dit nog altijd niet gevonden...

ReRAM heeft nu helaas nog meer dan voldoende problemen: moeilijk goedkoper te maken dan NAND flashgeheugen, hoge schrijfstroom, variabiliteit, ...

quote:Use of porous silicon oxide reduces forming voltage, improves manufacturability

HOUSTON — (July 10, 2014) — Rice University’s breakthrough silicon oxide technology for high-density, next-generation computer memory is one step closer to mass production, thanks to a refinement that will allow manufacturers to fabricate devices at room temperature with conventional production methods.

This scanning electron microscope image and schematic show the design and composition of new RRAM memory devices based on porous silicon oxide that were created at Rice University. Credit: Tour Group/Rice University

First discovered five years ago, Rice’s silicon oxide memories are a type of two-terminal, “resistive random-access memory” (RRAM) technology. In a new paper available online in the American Chemical Society journal Nano Letters, a Rice team led by chemist James Tour compared its RRAM technology to more than a dozen competing versions.

“This memory is superior to all other two-terminal unipolar resistive memories by almost every metric,” Tour said. “And because our devices use silicon oxide — the most studied material on Earth — the underlying physics are both well-understood and easy to implement in existing fabrication facilities.” Tour is Rice’s T.T. and W.F. Chao Chair in Chemistry and professor of mechanical engineering and nanoengineering and of computer science.

Tour and colleagues began work on their breakthrough RRAM technology more than five years ago. The basic concept behind resistive memory devices is the insertion of a dielectric material — one that won’t normally conduct electricity — between two wires. When a sufficiently high voltage is applied across the wires, a narrow conduction path can be formed through the dielectric material.

This illustration depicts the rewriteable crystalline filament pathway in Rice University's porous silicon oxide RRAM memory devices. Credit: Tour Group/Rice University

The presence or absence of these conduction pathways can be used to represent the binary 1s and 0s of digital data. Research with a number of dielectric materials over the past decade has shown that such conduction pathways can be formed, broken and reformed thousands of times, which means RRAM can be used as the basis of rewritable random-access memory.

RRAM is under development worldwide and expected to supplant flash memory technology in the marketplace within a few years because it is faster than flash and can pack far more information into less space. For example, manufacturers have announced plans for RRAM prototype chips that will be capable of storing about one terabyte of data on a device the size of a postage stamp — more than 50 times the data density of current flash memory technology.

The key ingredient of Rice’s RRAM is its dielectric component, silicon oxide. Silicon is the most abundant element on Earth and the basic ingredient in conventional microchips. Microelectronics fabrication technologies based on silicon are widespread and easily understood, but until the 2010 discovery of conductive filament pathways in silicon oxide in Tour’s lab, the material wasn’t considered an option for RRAM.

Since then, Tour’s team has raced to further develop its RRAM and even used it for exotic new devices like transparent flexible memory chips. At the same time, the researchers also conducted countless tests to compare the performance of silicon oxide memories with competing dielectric RRAM technologies.

Rice University postdoctoral researcher Gunuk Wang, left, and chemist James Tour have demonstrated new techniques for using porous silicon oxide to make robust RRAM memory chips that can be easily manufactured with existing fabrication techniques. Credit: Jeff Fitlow/Rice University

“Our technology is the only one that satisfies every market requirement, both from a production and a performance standpoint, for nonvolatile memory,” Tour said. “It can be manufactured at room temperature, has an extremely low forming voltage, high on-off ratio, low power consumption, nine-bit capacity per cell, exceptional switching speeds and excellent cycling endurance.”

In the latest study, a team headed by lead author and Rice postdoctoral researcher Gunuk Wang showed that using a porous version of silicon oxide could dramatically improve Rice’s RRAM in several ways. First, the porous material reduced the forming voltage — the power needed to form conduction pathways — to less than two volts, a 13-fold improvement over the team’s previous best and a number that stacks up against competing RRAM technologies. In addition, the porous silicon oxide also allowed Tour’s team to eliminate the need for a “device edge structure.”

“That means we can take a sheet of porous silicon oxide and just drop down electrodes without having to fabricate edges,” Tour said. “When we made our initial announcement about silicon oxide in 2010, one of the first questions I got from industry was whether we could do this without fabricating edges. At the time we could not, but the change to porous silicon oxide finally allows us to do that.”

This electron microscope image shows the surface of the nanoporous silicon-oxide material used in Rice University's new RRAM memory devices. The red areas highlight gaps, or voids, in the material's amorphous silicon-oxide coating. Credit: Tour Group/Rice University

Wang said, “We also demonstrated that the porous silicon oxide material increased the endurance cycles more than 100 times as compared with previous nonporous silicon oxide memories. Finally, the porous silicon oxide material has a capacity of up to nine bits per cell that is highest number among oxide-based memories, and the multiple capacity is unaffected by high temperatures.”

Tour said the latest developments with porous silicon oxide — reduced forming voltage, elimination of need for edge fabrication, excellent endurance cycling and multi-bit capacity — are extremely appealing to memory companies.

“This is a major accomplishment, and we’ve already been approached by companies interested in licensing this new technology,” he said.

Study co-authors — all from Rice — include postdoctoral researcher Yang Yang; research scientist Jae-Hwang Lee; graduate students Vera Abramova, Huilong Fei and Gedeng Ruan; and Edwin Thomas, the William and Stephanie Sick Dean of Rice’s George R. Brown School of Engineering, professor in mechanical engineering and materials science and in chemical and biomolecular engineering.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

HP wil memristors gebruiken in hun nieuwe non von Neuman computer architecture

TheMachine

Dit is een serieus project waar veel geld in gestoken wordt. Ik ga er vanuit dat de memristor technologie ondertussen goed genoeg is om de stap van lab naar fab te maken.

TheMachine

Dit is een serieus project waar veel geld in gestoken wordt. Ik ga er vanuit dat de memristor technologie ondertussen goed genoeg is om de stap van lab naar fab te maken.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:Resistive RAM nears launch: Still the most likely candidate to replace NAND flash

December 22, 2014

It’s been a while since we checked in on Crossbar, the next-generation memory company working on a NAND flash replacement. The company’s resistive RAM (RRAM or ReRAM) technology stores data by creating resistance in a circuit rather than trapping electrons within a cell. Now, the company has announced that it’s moving towards commercializing its designs. That means it’s proven that it can build hardware at existing foundries and can seek vendors to bring solutions to market.

There are several intrinsic advantages to ReRAM as compared to NAND flash. NAND has limited endurance, its lifespan degrades as process nodes shrink and cells become smaller, and the amount of error-correction required at each new node is steadily increasing. Performance gains have slowed since clocking NAND faster also tends to cause it to degrade, and the bulk of improvements are now delivered by improving either the NAND controller or the system interface — not the underlying performance of the NAND itself.

ReRAM solves many of these problems. Unlike NAND, it doesn’t need to be erased before its programmed, and it’s much faster than NAND by multiple metrics. It also consumes less power — Crossbar claims that NAND requires 1360 picojoules per cell to program, while RRAM cuts this to just 64 picojoules per cell. Programming power is just one aspect to overall SSD power consumption, but the company also claims that its technology supports storing two bits of data per cell (analogous to MLC NAND) and can be stacked into 3D

The company also claims that its technology can be used to reduce the complexity of the microcontroller itself — a significant potential advantage as this is one area where complexity and cost have been increasing as the task of flash management becomes more complicated.

Commercialization of consumer hardware, however, remains some time away. Crossbar has demonstrated that its designs can scale up into the terascale, but that doesn’t mean it’s ready to bring products at that density to market.

The firm is now licensing to ASIC, FPGA, and SoC developers, with samples arriving in 2015. Early expected target applications are the embedded and low-level applications shown in the chart above, where very little storage is required and low-power operation is essential.

One thing that hasn’t changed is the long-term roadmap for actual NAND flash replacement. Here’s where the realities of economic scaling come home to roost. Samsung, Intel, Micron — these companies have invested tens of billions of dollars into NAND production, and they aren’t going to shift to a new standard on a dime. For all that the tech industry likes to pride itself on rapidly adopting the latest and greatest technology, the truth is far different — the most successful products in computing are those that extend previous work in a cost-effective manner. Come-from-behind overtake maneuvers are actually quite rare, which is one reason why storage mediums tend to live for decades even when faster solutions are available in the market.

Right now, 3D NAND flash (Samsung calls it V-NAND) will drive the market from at least 2015 to 2018. That doesn’t mean we won’t see RRAM in consumer or enterprise applications — the market has snapped up more-expensive NAND flash solutions that leverage standards like PCI Express or the upcoming NVMe, particularly when these products can enable faster response times for high-frequency stock trading or other latency-critical applications. RRAM may not “feel” much faster than NAND, but it has the potential to provide better response times at latencies that matter to computers, and that’s enough of a reason for certain segments to adopt the equipment.

Earlier this year, we covered advances in other NAND flash replacements, such as phase change memory (PCM). These designs have demonstrated substantially improved performance compared to NAND, but also face significant scaling challenges and cost concerns. RRAM uses conventional CMOS hardware and can operate at scales down to 5nm. NAND flash, in contrast, isn’t expected to scale below 10nm on even the most optimistic roadmaps, and it’s not certain it will even get that low.

3D NAND will extend this further by allowing companies to step back up to higher nodes (Samsung’s current V-NAND is built on 40nm process technology). It’s not necessarily fair to call that a stopgap when it could slap 5-10 years on NAND scaling, but it’s still a long-term functional limitation. We’re going to need to replace flash with some alternate form of memory in the long term if we want to continue to improve power consumption and scale compute capability upwards, and right now RRAM looks like the most practical near-term option.

Het zal mij benieuwen of na Panasonic nu ook Crossbar komt met microcontrollers waarin RRAM is geintegreerd. Interessant zijn ook FPGA's met RRAM. Nu gebruiken de meeste FPGA's RAM/EEPROM om de LUT's, Fuses en links te defineren. Met RRAM is het instant on en direct functioneel. 3D-NAND kan nog wel even door maar jammer genoeg remt dat de ontwikkeling van RRAM. Dat terwijl RRAM vooral voor kunstmatige intelligentie juist zo tof is omdat het redelijk eenvoudig is er hoogwaardige neurale netwerken mee te implementeren. Wie met de RRAM microcontrollers komt is me niet duidelijk maar Atmel en Microchip zouden kandidaten kunnen zijn. Hopelijk Atmel zodat we straks Arduino-bordjes met RRAM kunnen kopen om mee te hobbyen

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Researchers create first neural-network chip built just with memristors

http://phys.org/news/2015(...)uilt-memristors.htmlquote:(Phys.org)—A team of researchers working at the University of California (and one from Stony Brook University) has for the first time created a neural-network chip that was built using just memristors. In their paper published in the journal Nature, the team describes how they built their chip and what capabilities it has.

Memristors may sound like something from a sci-fi movie, but they actually exist—they are electronic analog memory devices that are modeled on human neurons and synapses. Human consciousness, some believe, is in reality, nothing more than an advanced form of memory retention and processing, and it is analog, as opposed to computers, which of course are digital. The idea for memristors was first dreamed up by University of California professor Leon Chua back in 1971, but it was not until a team working at Hewlett-Packard in 2008, first built one. Since then, a lot of research has gone into studying the technology, but until now, no one had ever built a neural-network chip based exclusively on them.

Up till now, most neural networks have been software based, Google, Facebook and IBM, for example, are all working on computer systems running such learning networks, mostly meant to pick faces out of a crowd, or return an answer based on a human phrased question. While the gains in such technology have been obvious, the limiting factor is the hardware—as neural networks grow in size and complexity, they begin to tax the abilities of even the fastest computers. The next step, most in the field believe, is to replace transistors with memristors—each on its own is able to learn, in ways similar to the way neurons in the brain learn when presented with something new. Putting them on a chip would of course reduce the overhead needed to run such a network.

The new chip, the team reports, was created using transistor-free metal-oxide memristor crossbars and represents a basic neural network able to perform just one task—to learn and recognize patterns in very simple 3 × 3-pixel black and white images. The experimental chip, they add, is an important step towards the creation of larger neural networks that tap the real power of remristors. It also makes possible the idea of building computers in lock-step with advances in research looking into discovering just how exactly our neurons work at their most basic level.

Robert Moog died for our synths

Ah tof IBM heeft toch al een hele simulatie van zo'n chip lopen en zelfs al software ervoor als ze er ooit zijn... dit is dus een eerste stap in die richting om ze echt te maken.quote:Op woensdag 13 mei 2015 14:06 schreef Gehenna het volgende:

Researchers create first neural-network chip built just with memristors

[ afbeelding ]

[..]

http://phys.org/news/2015(...)uilt-memristors.html

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

quote:Op woensdag 13 mei 2015 15:10 schreef Bosbeetle het volgende:

[..]

Ah tof IBM heeft toch al een hele simulatie van zo'n chip lopen en zelfs al software ervoor als ze er ooit zijn... dit is dus een eerste stap in die richting om ze echt te maken.

Robert Moog died for our synths

Zal denk ik nog wel lang in het supercomputer domein blijven hangen.quote:Op woensdag 13 mei 2015 15:18 schreef Gehenna het volgende:

[..]Dit kan wel iets heel groots gaan worden

(nu alleen nog een taak verzinnen, schaken zijn computers al beter in

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

Een situatieschets kunnen maken aan de hand van een foto.quote:Op woensdag 13 mei 2015 15:25 schreef Bosbeetle het volgende:

[..]

Zal denk ik nog wel lang in het supercomputer domein blijven hangen.

(nu alleen nog een taak verzinnen, schaken zijn computers al beter indus dan moet het iets anders worden....)

Een klein kind zou al kunnen nagaan dat de vaas hierboven waarschijnlijk is omgegooid door de cat, maar op dit moment er is er gewoon geen computer (algoritme) die zoiets kan nagaan..

Robert Moog died for our synths

De vaas is daar neergelegd voor de foto, de kat is een "modelpoes" die speciaal is geinstrueerd voor deze shoot en dat plantenbakje op de kruk is lelijk...quote:Op woensdag 13 mei 2015 15:42 schreef Gehenna het volgende:

[..]

Een situatieschets kunnen maken aan de hand van een foto.

[ afbeelding ]

Een klein kind zou al kunnen nagaan dat de vaas hierboven waarschijnlijk is omgegooid door de cat, maar op dit moment er is er gewoon geen computer (algoritme) die zoiets kan nagaan..

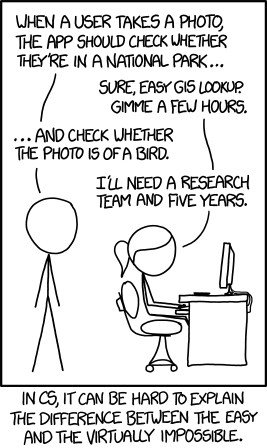

(was hier niet een keer een xkcd over)

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

Ja een klein kind is ook gewoon dom natuurlijk, daarom juist: neurale-computersquote:Op woensdag 13 mei 2015 15:45 schreef Bosbeetle het volgende:

[..]

De vaas is daar neergelegd voor de foto, de kat is een "modelpoes" die speciaal is geinstrueerd voor deze shoot en dat plantenbakje op de kruk is lelijk...

quote:(was hier niet een keer een xkcd over)

Deze weet ik nog, maar volgens mij nog wel vaker toch?

Robert Moog died for our synths

Het was een what if die alleen in zn boek stond...quote:Op woensdag 13 mei 2015 15:47 schreef Gehenna het volgende:

[..]

Ja een klein kind is ook gewoon dom natuurlijk, daarom juist: neurale-computers

[..]

[ afbeelding ]

Deze weet ik nog, maar volgens mij nog wel vaker toch?

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

http://tweakers.net/nieuw(...)bjecten-op-foto.htmlquote:Op woensdag 13 mei 2015 15:47 schreef Gehenna het volgende:

[..]

Ja een klein kind is ook gewoon dom natuurlijk, daarom juist: neurale-computers

[..]

[ afbeelding ]

Deze weet ik nog, maar volgens mij nog wel vaker toch?

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

Ja en je had ook Google Glass al een tijdje natuurlijk, maar er zit wel verschil in tussen 'een object herkennen', en een 'situatie kunnen beschrijven' natuurlijkquote:Op donderdag 14 mei 2015 09:44 schreef Bosbeetle het volgende:

[..]

http://tweakers.net/nieuw(...)bjecten-op-foto.html

Robert Moog died for our synths

Zeker, een stapje per keer. Ben echt benieuwd wat ze zo'n neurale computer kunnen laten doen.quote:Op vrijdag 15 mei 2015 10:22 schreef Gehenna het volgende:

[..]

Ja en je had ook Google Glass al een tijdje natuurlijk, maar er zit wel verschil in tussen 'een object herkennen', en een 'situatie kunnen beschrijven' natuurlijk

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

Gezien dat onze eigen neurale netwerken hier zo extreem goed in zijn, verwacht ik wel redelijk snel leuke resultaten eigenlijkquote:Op vrijdag 15 mei 2015 10:26 schreef Bosbeetle het volgende:

[..]

Zeker, een stapje per keer. Ben echt benieuwd wat ze zo'n neurale computer kunnen laten doen.

Robert Moog died for our synths

Onze eigen neurale netwerken zijn wel een stukje ingewikkelder dan een memristor... Ik denk eerder dat ze deze systemen gaan gebruiken om onze eigen neuronen beter te leren begrijpen. Leuk startpunt zou C.elegans zijn een klein wormpje die maar een paar (302) neuronen heeft en toch al wel wat taken kan doen, erg tof om te kijken hoe dicht we daar bij in de buurt kunnen komen.quote:Op vrijdag 15 mei 2015 10:32 schreef Gehenna het volgende:

[..]

Gezien dat onze eigen neurale netwerken hier zo extreem goed in zijn, verwacht ik wel redelijk snel leuke resultaten eigenlijk

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

De startpost stamt uit 2010 maar als ik het goed begrijp worden deze technieken nog (steeds) niet ingezet voor consumenten producten?

1/10 Van de rappers dankt zijn bestaan in Amerika aan de Nederlanders die zijn voorouders met een cruiseschip uit hun hongerige landen ophaalde om te werken op prachtige plantages.

"Oorlog is de overtreffende trap van concurrentie."

"Oorlog is de overtreffende trap van concurrentie."

Het begint te komenquote:Op vrijdag 15 mei 2015 13:59 schreef icecreamfarmer_NL het volgende:

De startpost stamt uit 2010 maar als ik het goed begrijp worden deze technieken nog (steeds) niet ingezet voor consumenten producten?

En mochten we vallen dan is het omhoog. - Krang (uit: Pantani)

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

My favourite music is the music I haven't yet heard - John Cage

Water: ijskoud de hardste - Gehenna

Dat heb je goed begrepenquote:Op vrijdag 15 mei 2015 13:59 schreef icecreamfarmer_NL het volgende:

De startpost stamt uit 2010 maar als ik het goed begrijp worden deze technieken nog (steeds) niet ingezet voor consumenten producten?

|

|

Op

Op