W&T Wetenschap & Technologie

Een plek om te discussiëren over wetenschappelijke onderwerpen, wetenschappelijke problemen, technologische projecten en grootse uitvindingen.

Ik wil graag een nieuw fundamenteel electronische component vermelden dat mogelijk van zeer grote invloed gaat zijn, de memristor. We hadden de spoel(inductie), condensator(capaciteit) en de weerstand,na 150 jaar is daar nu de memristor als 4e element bijgekomen.

Symbool van de memristor

Wat maakt nu de memristor nu zo bijzonder?

Het woord zegt het al. Het is een combinatie van geheugen en weerstand. Als de spanning boven de drempelspanning van een speciaal type halfgeleider junctie komt verplaatsen zich ionische ladingsdragers en veranderd de weerstand. Het proces is omkeerbaar dus de weerstand kan zowel verhoogt danwel verlaagt worden naar gelang de stoom door en polariteit over de junctie.

Tot nu toe bestond er geen component die zelfstandig over een geheugenfunctie beschikte. Er zijn altijd combinaties nodig van meerdere componenten zoals in ram-geheugen de combinatie condensator, weerstand en transistor. Dan nog zijn deze combinaties verre van ideaal. RAM geheugen is vluchtig en er is continu stroomverbruik vanwege de refresh. Flash is traag en zelfdestructief, het kan slecht een beperkt aantal malen herschreven worden. SRAM kost veel componenten, 5 a 6 transistors en meerdere weerstanden en ook daar is het geheugen weg als de spanning wegvalt. EEPROM is een combinatie van SRAM en een condensator die heel langzaam zijn lading(geheugen) verliest. Ook hierbij zijn er veel componenten nodig.

Een ideale memristor heeft:

Zeer hoge responstijden, afhankelijk van de migratiesnelheid van de ladingdragers.

Geen zelfdestructie bij herhaalt herschrijven.

Verliest nooit zijn geheugen.

Een ideale memristor bestaat echter niet maar in hoevere wordt die benaderd in de praktijk?

Wat de responstijden betreft zit er nogal een verschil in het schrijven en uitlezen. Bij het schrijven moeten ionische ladingdragers zich verplaatsen en daarbij blijkt het om cm tot meters per seconde te gaan. Dan nog hebben we het over een mogelijk haalbaar nanoseconden bereik. Het uitlezen gaat via de gebruikelijke ladingsdragers, gaten en elektronen en overstijgt het nanoseconden bereik.

Zelfdestructie bij herschrijven treedt op vanwege het gebruik van ionische ladingsdragers zoals ook bij Flash. Het effect kan hier echter veel verder teruggebracht worden, miljoenen tot miljarden herschijvingen lijken tot de mogelijkheden te behoren.

Wat het geheugen betreft zijn er inderdaad substraten die in de praktijk niet merkbaar aan geheugen verliezen. Huidige modellen tonen aan dat ze alle gebruikelijke vormen van geheugen ver overstijgt. Dit omdat de energie die nodig is om de ionische ladingdragers terug te verplaatsen te hoog is om spontaan plaats te vinden.

Wat zijn de voordelen van een memristor?

Het is permanent geheugen.

Laag energieverbruik, zowel bij schrijven als lezen.

Hoge leessnelheid, geen waitstates zoals bij RAM.

Is zowel digitaal als analoog toepasbaar.

Weinig componenten nodig voor een geheugencel.

Een neurale synaps met zeer hoge resolutie is te vervaardigen met slechts 1 transistor en een memristor gekoppeld aan de basisterminal ipv de huidige tientallen transistoren, weerstanden en condensators.

Nadelen:

Het is een nano fenomeen en dus hebben we het over nanometerschaal componenten dientengevolge zijn de stuur en leesstromen zeer gering. Verwacht dus niet te snel dat je een memristor kan kopen in de electronica winkel. Op termijn zal het waarschijnlijk in de vorm van IC's zoals microcontrollers geimplementeerd worden en verkrijgbaar zijn.

Material deformation: Dit is het gevolg van het gebruik van ionische ladingsdragers en is mbv nanoscale microscopen zelfs direct waar te nemen. Er zal een tradeoff zijn tussen de schrijfsnelheid en het aantal malen herhaald herschrijven. Hogere spanningen doen de migratiesnelheid van ionische ladingdragers exponentieel toenemen maar leidt tot versterkte deformatie en dus een lager aantal mogelijke herschrijvingen. Dit blijkt ook sterk substraat afhankelijk te zijn. Si/Ag substraten lijken zeer bruikbaar en zijn al direct toepasbaar in IC fabrieken. De race naar het optimale substraat is nog maar net begonnen.

WikiMemristor

Recente lezing memristor

Er staat een aantal lezing over de memristor in de playlists van citrisuc

Ik denk dat de memristor die bij toeval is ontdekt in HPlabs 1 van de grootste doorbraken is op het gebied van nanotechnologie en electronica van de afgelopen jaren en misschien wel van de komende jaren. Mogelijk vergelijkbaar met de impact van de transistor

[ Bericht 0% gewijzigd door Digi2 op 21-03-2010 16:21:23 ]

Symbool van de memristor

Wat maakt nu de memristor nu zo bijzonder?

Het woord zegt het al. Het is een combinatie van geheugen en weerstand. Als de spanning boven de drempelspanning van een speciaal type halfgeleider junctie komt verplaatsen zich ionische ladingsdragers en veranderd de weerstand. Het proces is omkeerbaar dus de weerstand kan zowel verhoogt danwel verlaagt worden naar gelang de stoom door en polariteit over de junctie.

Tot nu toe bestond er geen component die zelfstandig over een geheugenfunctie beschikte. Er zijn altijd combinaties nodig van meerdere componenten zoals in ram-geheugen de combinatie condensator, weerstand en transistor. Dan nog zijn deze combinaties verre van ideaal. RAM geheugen is vluchtig en er is continu stroomverbruik vanwege de refresh. Flash is traag en zelfdestructief, het kan slecht een beperkt aantal malen herschreven worden. SRAM kost veel componenten, 5 a 6 transistors en meerdere weerstanden en ook daar is het geheugen weg als de spanning wegvalt. EEPROM is een combinatie van SRAM en een condensator die heel langzaam zijn lading(geheugen) verliest. Ook hierbij zijn er veel componenten nodig.

Een ideale memristor heeft:

Zeer hoge responstijden, afhankelijk van de migratiesnelheid van de ladingdragers.

Geen zelfdestructie bij herhaalt herschrijven.

Verliest nooit zijn geheugen.

Een ideale memristor bestaat echter niet maar in hoevere wordt die benaderd in de praktijk?

Wat de responstijden betreft zit er nogal een verschil in het schrijven en uitlezen. Bij het schrijven moeten ionische ladingdragers zich verplaatsen en daarbij blijkt het om cm tot meters per seconde te gaan. Dan nog hebben we het over een mogelijk haalbaar nanoseconden bereik. Het uitlezen gaat via de gebruikelijke ladingsdragers, gaten en elektronen en overstijgt het nanoseconden bereik.

Zelfdestructie bij herschrijven treedt op vanwege het gebruik van ionische ladingsdragers zoals ook bij Flash. Het effect kan hier echter veel verder teruggebracht worden, miljoenen tot miljarden herschijvingen lijken tot de mogelijkheden te behoren.

Wat het geheugen betreft zijn er inderdaad substraten die in de praktijk niet merkbaar aan geheugen verliezen. Huidige modellen tonen aan dat ze alle gebruikelijke vormen van geheugen ver overstijgt. Dit omdat de energie die nodig is om de ionische ladingdragers terug te verplaatsen te hoog is om spontaan plaats te vinden.

Wat zijn de voordelen van een memristor?

Het is permanent geheugen.

Laag energieverbruik, zowel bij schrijven als lezen.

Hoge leessnelheid, geen waitstates zoals bij RAM.

Is zowel digitaal als analoog toepasbaar.

Weinig componenten nodig voor een geheugencel.

Een neurale synaps met zeer hoge resolutie is te vervaardigen met slechts 1 transistor en een memristor gekoppeld aan de basisterminal ipv de huidige tientallen transistoren, weerstanden en condensators.

Nadelen:

Het is een nano fenomeen en dus hebben we het over nanometerschaal componenten dientengevolge zijn de stuur en leesstromen zeer gering. Verwacht dus niet te snel dat je een memristor kan kopen in de electronica winkel. Op termijn zal het waarschijnlijk in de vorm van IC's zoals microcontrollers geimplementeerd worden en verkrijgbaar zijn.

Material deformation: Dit is het gevolg van het gebruik van ionische ladingsdragers en is mbv nanoscale microscopen zelfs direct waar te nemen. Er zal een tradeoff zijn tussen de schrijfsnelheid en het aantal malen herhaald herschrijven. Hogere spanningen doen de migratiesnelheid van ionische ladingdragers exponentieel toenemen maar leidt tot versterkte deformatie en dus een lager aantal mogelijke herschrijvingen. Dit blijkt ook sterk substraat afhankelijk te zijn. Si/Ag substraten lijken zeer bruikbaar en zijn al direct toepasbaar in IC fabrieken. De race naar het optimale substraat is nog maar net begonnen.

WikiMemristor

Recente lezing memristor

Er staat een aantal lezing over de memristor in de playlists van citrisuc

Ik denk dat de memristor die bij toeval is ontdekt in HPlabs 1 van de grootste doorbraken is op het gebied van nanotechnologie en electronica van de afgelopen jaren en misschien wel van de komende jaren. Mogelijk vergelijkbaar met de impact van de transistor

[ Bericht 0% gewijzigd door Digi2 op 21-03-2010 16:21:23 ]

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Dit gaat er inderdaad voor zorgen dat de rekenkracht van de CPU de komende jaren nog ongestoord kan verdubbelen ieder jaar.

Mooi dat we nu eindelijk een 3e dimensie kunnen gaan gebruiken bij het maken van CPU's.

Hoop dat dit vrij vlot geïmplementeerd gaat worden in consumenten producten, de impact zal enorm zijn!

Mooi dat we nu eindelijk een 3e dimensie kunnen gaan gebruiken bij het maken van CPU's.

Hoop dat dit vrij vlot geïmplementeerd gaat worden in consumenten producten, de impact zal enorm zijn!

Dit klinkt interessant, maar kan je je conclusie toelichten?quote:Op zondag 21 maart 2010 15:40 schreef Refragmental het volgende:

Dit gaat er inderdaad voor zorgen dat de rekenkracht van de CPU de komende jaren nog ongestoord kan verdubbelen ieder jaar.

Mooi dat we nu eindelijk een 3e dimensie kunnen gaan gebruiken bij het maken van CPU's.

Hoop dat dit vrij vlot geïmplementeerd gaat worden in consumenten producten, de impact zal enorm zijn!

Hoe zorgt de memristor ervoor dat wij nu een 3e dimensie kunnen gaan gebruiken bij het maken van CPU's ?

http://www.youtube.com/us(...)638C02/3/Z5UTRTOfgo4quote:Op zondag 21 maart 2010 18:44 schreef Onverlaatje het volgende:

[..]

Dit klinkt interessant, maar kan je je conclusie toelichten?

Hoe zorgt de memristor ervoor dat wij nu een 3e dimensie kunnen gaan gebruiken bij het maken van CPU's ?

In deze lezing uit de OP wordt uitgelegd hoe ze de memristor bovenop de huidige transistor kunnen plaatsen, en niet 1,2 of 3 lagen maar mogelijk duizend lagen.

Het hier aangehaalde voorbeeld gaat over een mogelijke vervanger van flashram. Memristors kunnen niet miljarden xen per seconde herschreven worden zoals in een CPU gebruikelijk is. In minder dan 1 seconde zou hij al defect raken. Directe toepassingen in een CPU zie ik als beperkt tot configuratie switsches welke slechts zelden veranderd worden. Een mogelijke toepassing zouden herprogrammeerbare logic gates kunnen zijn binnen een deel van de CPU. Een soort van FPGA in een CPU. Deze mogelijkheden worden al onderzocht en kunnen tot een sneller en efficienter CPU leiden. Nadeel is dat er een extra interpreter of precompiler nodig zal zijn binnen het Operating System. De instructie CPUID is niet meer afdoende om de software te verduidelijken welke configuraties/instructies ondersteunt worden omdat die telkens kunnen wijzigen. Dan nog is er maar ruimte voor een beperkt aantal herconfiguraties in het geval van een memristorFPGA binnen de levensduur van zo'n CPU.quote:Op zondag 21 maart 2010 19:45 schreef Refragmental het volgende:

http://www.youtube.com/us(...)638C02/3/Z5UTRTOfgo4

In deze lezing uit de OP wordt uitgelegd hoe ze de memristor bovenop de huidige transistor kunnen plaatsen, en niet 1,2 of 3 lagen maar mogelijk duizend lagen.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Maar als ik het goed begrijp kan er nu wel een specifiek neuraal netwerk CPU gemaakt worden.

Wat zouden de toepassingen van dergelijke CPU's zijn in het dagelijks leven?

Verbeterde database searches? Een just in time compiler, gebakken in de CPU zelf?

Wat zouden de toepassingen van dergelijke CPU's zijn in het dagelijks leven?

Verbeterde database searches? Een just in time compiler, gebakken in de CPU zelf?

Memristors zijn bijna ideaal voor neurale netwerken en wat het helemaal tof maakt is dat Titaanoxide memristors zelfs biocompatibel zijn. Titaanoxide wordt niet afgestoten, een interface mogelijkheid met biologische neuronen is mogelijk. Neurale netwerken zijn goed in patroonherkenning dus in dergelijke toepassingen zijn ze te vinden. Voor klassieke computers is dat juist zeer lastig gebleken.quote:Op maandag 22 maart 2010 13:41 schreef Onverlaatje het volgende:

Maar als ik het goed begrijp kan er nu wel een specifiek neuraal netwerk CPU gemaakt worden.

Wat zouden de toepassingen van dergelijke CPU's zijn in het dagelijks leven?

Verbeterde database searches? Een just in time compiler, gebakken in de CPU zelf?

Voor database searches zijn goede algoritmes De huidige computers, en zeker multicoresystemen zijn daar sterk in vandaar het succes van zoeksystemen als google etc. Als het er om gaat gezichten te herkennen in een database met foto's, daar zijn juist neurale netwerken sterk in. Neurale netwerken dienen doorgaans getraind te worden of de "gewichten" van de synapsen van de juiste waarden voorzien. Compilers dienen te verdwijnen naar OS niveau of daar zelfs onder. Een programma dient geinterpreteerd te worden naar een specifieke CPU/GPU/IOchipset configuratie. Omdat dat nu nog niet gebeurt is de performance eigenlijk abominabel te noemen tov de hardware mogelijkheden

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Daar zullen gehandicapten en blinden bijzonder blij mee zijn.quote:Titaanoxide wordt niet afgestoten, een interface mogelijkheid met biologische neuronen is mogelijk. Neurale netwerken zijn goed in patroonherkenning dus in dergelijke toepassingen zijn ze te vinden.

Dan zou er een compiler configuration interface geschreven dienen te worden, zodat een CPU kan vertellen wat de logica achter de instructies is.quote:Een programma dient geinterpreteerd te worden naar een specifieke CPU/GPU/IOchipset configuratie. Omdat dat nu nog niet gebeurt is de performance eigenlijk abominabel te noemen tov de hardware mogelijkheden

Probleem is dat progs gecompileerd aangeleverd worden en om het op verschillende computer confs aan de praat te krijgen zijn diverse libraries zoals DLL's nodig en links naar drivers van GPU's, IOchipset etc.quote:Op maandag 22 maart 2010 18:00 schreef Onverlaatje het volgende:

Dan zou er een compiler configuration interface geschreven dienen te worden, zodat een CPU kan vertellen wat de logica achter de instructies is.

Dat is verre van optimaal, er ontstaan diverse interface tussenlagen die ook nog een bugs kunnen bevatten.

De juiste weg is. De installer checked de hardware en optimaliseert en compileert ter plaatse de executable naar de eigen conf. Drivers zijn dan niet meer nodig. Er zijn een aantal redenen waarom dit niet gebeurt.

Hardwarefabrikanten willen niet teveel in eigen keuken laten kijken. Vandaar vaak proprietary drivers. ATI/AMD en Intel geven vaak wel inzicht in de sourcecodes aan een selecte groep OS schrijvers zoals LINUX, ATI AMD doet dat pas sinds kort. Men geeft niet graag broncodes uit handen omdat die veel intellectuele ideeen/eigendommen bevatten. De prijs hiervoor is lompe inefficiente progs die ook nog eens buggie zijn. Bovendien zou je een herinstall moeten doen indien je bijv je grafische kaart/GPU vervangt. Dit kan je ondervangen door de compiler/optimiser in je OS te integreren. Die kan dan bij een confchange automatisch opnieuw compileren.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

De oplossing is dan dat een bytecode compiler generieke (tussen verschillende processoren) code voor te laten compileren naar generieke machinecode en tussen deze code blokken bytecode aan te geven welke hercompileert dienen te worden naar CPU specifieke instructiesets. Zo kan je bedrijfsgevoelige code verdelen tussen blokken processorgenerieke code en te optimaliseren bytecode en zo dus 'obfuscaten' terwijl je wel geoptimaliseerde code laat uitvoeren.quote:Op maandag 22 maart 2010 19:52 schreef Digi2 het volgende:

[..]

Probleem is dat progs gecompileerd aangeleverd worden en om het op verschillende computer confs aan de praat te krijgen zijn diverse libraries zoals DLL's nodig en links naar drivers van GPU's, IOchipset etc.

Dat is verre van optimaal, er ontstaan diverse interface tussenlagen die ook nog een bugs kunnen bevatten.

De juiste weg is. De installer checked de hardware en optimaliseert en compileert ter plaatse de executable naar de eigen conf. Drivers zijn dan niet meer nodig. Er zijn een aantal redenen waarom dit niet gebeurt.

Hardwarefabrikanten willen niet teveel in eigen keuken laten kijken. Vandaar vaak proprietary drivers. ATI/AMD en Intel geven vaak wel inzicht in de sourcecodes aan een selecte groep OS schrijvers zoals LINUX, ATI AMD doet dat pas sinds kort. Men geeft niet graag broncodes uit handen omdat die veel intellectuele ideeen/eigendommen bevatten. De prijs hiervoor is lompe inefficiente progs die ook nog eens buggie zijn. Bovendien zou je een herinstall moeten doen indien je bijv je grafische kaart/GPU vervangt. Dit kan je ondervangen door de compiler/optimiser in je OS te integreren. Die kan dan bij een confchange automatisch opnieuw compileren.

Er bestaat wel al iets als 'precompiled headers' waarmee je zelf aan kan geven welke stukken code voorgecompileerd gedistribueerd kunnen worden. Maar dat wil je dan niet zelf, maar door de compiler laten beslissen en teruggeven aan een configure script zodat er een distributie project gegenereerd kan worden (geen idee of dit bestaat, ik denk nog van niet).

Toch kiezen hardware fabrikanten zoals van GPU's voor zover mij bekend nog niet voor deze weg. De combinatie van bytecode en JIT is zeker een optie die indien op grotere schaal toegepast tot hogere efficientie leidt.quote:Op maandag 22 maart 2010 21:46 schreef Onverlaatje het volgende:

De oplossing is dan dat een bytecode compiler generieke (tussen verschillende processoren) code voor te laten compileren naar generieke machinecode en tussen deze code blokken bytecode aan te geven welke hercompileert dienen te worden naar CPU specifieke instructiesets. Zo kan je bedrijfsgevoelige code verdelen tussen blokken processorgenerieke code en te optimaliseren bytecode en zo dus 'obfuscaten' terwijl je wel geoptimaliseerde code laat uitvoeren.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Ik heb sterk het idee dat je hier de transistor sterk tekort mee doetquote:Op zaterdag 20 maart 2010 12:07 schreef Digi2 het volgende:

We hadden de spoel(inductie), condensator(capaciteit) en de weerstand,na 150 jaar is daar nu de memristor als 4e element bijgekomen.

Are we not savages, innately destined to maim and kill?

Blame it on the environment, heredity or evolution: we're still responsible

Our intelligence may progress at geometric rates

Yet socially we remain belligerent neonates

Blame it on the environment, heredity or evolution: we're still responsible

Our intelligence may progress at geometric rates

Yet socially we remain belligerent neonates

Tja, de transistor wordt door wetenschappers net als de diode niet beschouwd als een fundamenteel element,quote:Op maandag 22 maart 2010 22:38 schreef YuckFou het volgende:

Ik heb sterk het idee dat je hier de transistor sterk tekort mee doet

Het is idd de vraag of het terecht is de memristor die status wel toe te dichten. Want een natuurkundige eenheid van memristance is er (nog) niet. Bij de weerstand luidt die in Ohm, Capaciteit in Farad en Inductie de Henry.

Als je het hebt over de impact van de transistor op ons dagelijks leven dan is de transistor zonder enige twijfel component nr1

[ Bericht 0% gewijzigd door Digi2 op 22-03-2010 23:18:27 ]

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:Siliciumgeheugen maakt kleiner productieprocedé eenvoudig

Door Willem de Moor, woensdag 1 september 2010 14:13, views: 1.597

De volgende stap naar nog kleinere productieprocedés zou dankzij siliciumgeheugen vrij eenvoudig zijn. Onderzoekers hebben eenvoudige geheugencellen ontwikkeld, die slechts bestaan uit silicium en aansluitingen.

Het nieuwe type geheugen werd ontwikkeld na observaties van dunne stroken grafiet, van ongeveer tien nanomoeter breed. Onder invloed van een stroompuls kon de strook worden gebroken en weer verbonden, wat het equivalent van een geheugenbit vormde. Nader onderzoek wees echter uit dat dit effect niet afhankelijk is van grafiet; ook silicium vertoont dit fenomeen. Aangezien silicium het hoofdbestanddeel van vrijwel alle processors is en goed in halfgeleiderproducten kan worden verwerkt, zou het siliciumgeheugen snel in productieprocessen kunnen worden geïntegreerd.

Het siliciumgeheugen werkt door een laagje siliciumoxide, een elektrische isolator, tussen twee lagen geleidend polykristallijn silicium te klemmen. Bij het aanbrengen van een stroom worden oxide-atomen van het silicium gestript, wat zorgt voor de vorming van geleidende siliciumkristallen. Eenmaal gevormd kunnen deze kristalsporen, net als het grafiet eerder, steeds opnieuw worden verbonden en verbroken. De lagen 'poly' dienen hierbij als elektrodes. Flashgeheugen is complexer en heeft drie elektrodes nodig.

De zo gevormde geheugenbits kunnen bijzonder eenvoudig worden geproduceerd en gezien hun samenstelling laten zij zich eenvoudig in bijvoorbeeld processors verwerken. Bovendien zijn de structuren zeer klein. De kristaldraden zijn tussen de vijf en tien nanometer groot, veel kleiner dan de featuresize waaraan de huidige geheugenproductietechnieken met hun 20 tot 30nm toe zijn. De siliciumoxide-geheugenbits zijn tevens in driedimensionale structuren te stapelen en schakelen in minder dan 100ns. De onderzoekers van de Rice-universiteit werken samen met verschillende bedrijven en hebben al een werkende prototype-geheugenchip met duizend elementen. Deze wordt nu getest.

Tweakers

Sciencedaily

Dit lijkt me een variant van de memristor alleen zo ver doorgevoerd dat het gereduceerde siliciumoxide kortsluiting veroorzaakt. Dat is blijkbaar mogelijk indien de laag siliciumoxide dun genoeg is. Uit onderzoek bij HP labs blijkt zilver/Si substraat superieur qua snelheid en herschrijbaarheid. Raar eigenlijk dat HP labs zelf niet op dit fenomeen gestuit zijn tijdens hun onderzoeken. Wellicht zagen zij de kortsluiting eerder als een "defect" om te vermijden.

Door silicium op te dampen op een metaallaag (meestal aluminium omdat dat niet door het silicium aan de wandel gaat zoals bij koper) en daarna te oxideren ontstaat een polysilicon laag gecoat met een nanolaag Oxide. Deze kan dan met een zilverlaag gecoat worden.

Dat zal wellicht het substraat van de volgende generatie geheugen zijn. Het brillante aan deze ontdekking is trouwens dat polysilicon een werkbare geheugencel opleverd. Hierdoor is stapelling van cellen een eitje. Normaal moet men monokristallijn Si gebruiken dat 1st uit een wafer gezaagd moet worden en intensief bewerkt voordat het gebruikt kan worden.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Dus dit wordt de nieuwe all-purpose datadrager van de 21ste eeuw?

Health In Harmony is een non-profitorganisatie die regenwoudgemeenschappen helpt met gezondheidszorg en duurzame inkomens in ruil voor bosbescherming, en zo tegelijk klimaatverandering en armoede aanpakt. - https://www.healthinharmony.org/

wow, als dit er komt dan kan ik toch zeggen tegen mijn vrienden dat ik erbij was toen het bedacht werd op FOK!

Trots lid van het 👿 Duivelse Viertal 👿

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Eh... waar lees je precies dat de TS een van de "ontdekkers/uitvinders" is?

Health In Harmony is een non-profitorganisatie die regenwoudgemeenschappen helpt met gezondheidszorg en duurzame inkomens in ruil voor bosbescherming, en zo tegelijk klimaatverandering en armoede aanpakt. - https://www.healthinharmony.org/

Hp gaat samenwerken met Hynix. Hynix zal de memristor technologie in produktie gaan nemen.

Ben benieuwd wat de specs gaan zijn van de 1e generatie IC's

Blijkbaar gaat de memristor technologie nu van lab naar fabrikage fase. Er is heel veel mogelijk met dit nieuwe element. Ik bedacht me dat je zelfs meerdere bits kunt opslaan in 1 enkele memristor. Dat kan door gebuik te maken van Schmitt Triggers of comparators. Hiermee kan je een memory controller voorzien van meerdere spanningsdrempel niveau's. De spanning over de memristor is in lineair verband met de weerstand. 8 bits per cel zou prima denkbaar zijn. Wat natuurlijk een enorm geheugen potentiaal opleverd.

De extra electronica levert wel wat extra vertraging op zoals ook bij multi level cell flashmemory (MLC).

De technologie van MLC is al behoorlijk ver mbt flashcellen. Een snelle introductie van deze methode voor memristors is te verwachten. Hieronder een PDF met enige uitleg over MLC versus SLC hier zie je ook het gebruik van de verschillende spanningsdrempels om meerder bits per cell te defineren.

Extra complicerende factoren bij flash. Het gaat hierbij om de floating gate van de Flashcell.

1. Precise charge placement

2. Precise charge sensing

Voor de memristor geldt .

1. Precise resistance placement

www.supertalent.com/datasheets/SLC_vs_MLC%20whitepaper.pdf

Dit geheugen zal dan wel MLMC Multi Level Memristance Cell of MLRC Multi Level Resistance Cell gaan heten

[ Bericht 6% gewijzigd door Digi2 op 13-09-2010 20:46:40 ]

Ben benieuwd wat de specs gaan zijn van de 1e generatie IC's

Blijkbaar gaat de memristor technologie nu van lab naar fabrikage fase. Er is heel veel mogelijk met dit nieuwe element. Ik bedacht me dat je zelfs meerdere bits kunt opslaan in 1 enkele memristor. Dat kan door gebuik te maken van Schmitt Triggers of comparators. Hiermee kan je een memory controller voorzien van meerdere spanningsdrempel niveau's. De spanning over de memristor is in lineair verband met de weerstand. 8 bits per cel zou prima denkbaar zijn. Wat natuurlijk een enorm geheugen potentiaal opleverd.

De extra electronica levert wel wat extra vertraging op zoals ook bij multi level cell flashmemory (MLC).

De technologie van MLC is al behoorlijk ver mbt flashcellen. Een snelle introductie van deze methode voor memristors is te verwachten. Hieronder een PDF met enige uitleg over MLC versus SLC hier zie je ook het gebruik van de verschillende spanningsdrempels om meerder bits per cell te defineren.

Extra complicerende factoren bij flash. Het gaat hierbij om de floating gate van de Flashcell.

1. Precise charge placement

2. Precise charge sensing

Voor de memristor geldt .

1. Precise resistance placement

www.supertalent.com/datasheets/SLC_vs_MLC%20whitepaper.pdf

Dit geheugen zal dan wel MLMC Multi Level Memristance Cell of MLRC Multi Level Resistance Cell gaan heten

[ Bericht 6% gewijzigd door Digi2 op 13-09-2010 20:46:40 ]

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Updated: HP, Hynix plan to launch memristor memory in 2013

Peter Clarke

10/6/2011 11:27 AM EDT

SEVILLE, Spain – The 'memristor' two-terminal non-volatile memory technology, in development at Hewlett Packard Co. since 2008, is on track to be in the market and taking share from flash memory within 18 months, according to Stan Williams, senior fellow at HP Labs.

"We have a lot of big plans for it and we're working with Hynix Semiconductor to launch a replacement for flash in the summer of 2013 and also to address the solid-state drive market," Williams told the audience of the International Electronics Forum, being held here.

A spokesperson for HP added that there is no definitive memristor product roadmap as yet, but confirmed that "HP has a goal to see memristor products by the end of 2013."

Williams said that the memristor metrics being achieved, in terms of energy to change a bit, read, write time, retention and endurance, were so compelling that flash replacement was effectively a done deal. "So in 2014/2015 we'll be going after DRAM and after that the SRAM market," Williams said indicating his confidence that the memristor would quickly become a universal memory.

Williams declined to discuss in detail the process technology, memory capacity or memory-effect material that Hewlett Packard and Hynix are working with. "We're running hundreds of wafers through a Hynix full-size fab. We're very happy with it." But Williams did disclose that the first commercial memory would be a multi-layer device.

When challenged over the cost of the technology, which would be the barrier to competing against the high-volume flash memory market, Williams said: "On a price per bit basis we could be an order of magnitude lower cost once you get the NRE [non-recurring expense] out of the way."

The memristor, named after the combination of memory and resistor, was originally a theoretical two-terminal device for which the electrical behavior was derived by Leon Chua in 1971. However, in 2008 researchers from HP published a paper in Nature that tied the hysterical I-V characteristics of two-terminal titanium oxide devices to the memristor prediction of Chua. "What we found is that moving a few atoms a fraction of a nanometer can change the resistance by three orders of magnitude," said Webb. "In fact many nanodevices have inherent memresistive behavior," he said.

HP has amassed some 500 patents around the memristor over the last three years. He also acknowledged that phase-change memory (PCM), Resistive RAM (RRAM) and other two-terminal memory devices are all memristor-type devices. Williams acknowledged that many other companies are working on metal-oxide resistive RAMs. He said that Samsung now has a bigger research team working on the technology than does HP.

Williams touted the cross-point nature of the memristor memory switch or resistive RAM device as a memory capacity advantage over flash memory. "Whatever the best in flash memory is, we'll be able to double that."

Implication logic and the synapse

Williams compared HP's resistive RAM technology against flash and claimed to meet or exceed the performance of flash memory in all categories. Read times are less than 10 nanoseconds and write/erase times are about 0.1-ns. HP is still accumulating endurance cycle data at 10^12 cycles and the retention times are measured in years, he said.

One of the best things about the memristor memory is that it is a simple structure made using materials that are already common in the world's wafer fabs making CMOS-compatible devices relatively straight forward, he said.

This creates the prospect of adding dense non-volatile memory as an extra layer on top of logic circuitry. "We could offer 2-Gbytes of memory per core on the processor chip. Putting non-volatile memory on top of the logic chip will buy us twenty years of Moore's Law, said Williams.

Further out Williams said the memristor could be used for computation under a scheme called "implication logic" in a fraction of the area taken up in CMOS by Boolean logic. In addition a memristor device is a good analog of the synapse in brain function.

In conclusion Williams stressed that HP would not be getting into the semiconductor components business but would seek to commercialize and then license the technology to all comers

HP-Hynix-to-launch-memristor-memory-2013

Peter Clarke

10/6/2011 11:27 AM EDT

SEVILLE, Spain – The 'memristor' two-terminal non-volatile memory technology, in development at Hewlett Packard Co. since 2008, is on track to be in the market and taking share from flash memory within 18 months, according to Stan Williams, senior fellow at HP Labs.

"We have a lot of big plans for it and we're working with Hynix Semiconductor to launch a replacement for flash in the summer of 2013 and also to address the solid-state drive market," Williams told the audience of the International Electronics Forum, being held here.

A spokesperson for HP added that there is no definitive memristor product roadmap as yet, but confirmed that "HP has a goal to see memristor products by the end of 2013."

Williams said that the memristor metrics being achieved, in terms of energy to change a bit, read, write time, retention and endurance, were so compelling that flash replacement was effectively a done deal. "So in 2014/2015 we'll be going after DRAM and after that the SRAM market," Williams said indicating his confidence that the memristor would quickly become a universal memory.

Williams declined to discuss in detail the process technology, memory capacity or memory-effect material that Hewlett Packard and Hynix are working with. "We're running hundreds of wafers through a Hynix full-size fab. We're very happy with it." But Williams did disclose that the first commercial memory would be a multi-layer device.

When challenged over the cost of the technology, which would be the barrier to competing against the high-volume flash memory market, Williams said: "On a price per bit basis we could be an order of magnitude lower cost once you get the NRE [non-recurring expense] out of the way."

The memristor, named after the combination of memory and resistor, was originally a theoretical two-terminal device for which the electrical behavior was derived by Leon Chua in 1971. However, in 2008 researchers from HP published a paper in Nature that tied the hysterical I-V characteristics of two-terminal titanium oxide devices to the memristor prediction of Chua. "What we found is that moving a few atoms a fraction of a nanometer can change the resistance by three orders of magnitude," said Webb. "In fact many nanodevices have inherent memresistive behavior," he said.

HP has amassed some 500 patents around the memristor over the last three years. He also acknowledged that phase-change memory (PCM), Resistive RAM (RRAM) and other two-terminal memory devices are all memristor-type devices. Williams acknowledged that many other companies are working on metal-oxide resistive RAMs. He said that Samsung now has a bigger research team working on the technology than does HP.

Williams touted the cross-point nature of the memristor memory switch or resistive RAM device as a memory capacity advantage over flash memory. "Whatever the best in flash memory is, we'll be able to double that."

Implication logic and the synapse

Williams compared HP's resistive RAM technology against flash and claimed to meet or exceed the performance of flash memory in all categories. Read times are less than 10 nanoseconds and write/erase times are about 0.1-ns. HP is still accumulating endurance cycle data at 10^12 cycles and the retention times are measured in years, he said.

One of the best things about the memristor memory is that it is a simple structure made using materials that are already common in the world's wafer fabs making CMOS-compatible devices relatively straight forward, he said.

This creates the prospect of adding dense non-volatile memory as an extra layer on top of logic circuitry. "We could offer 2-Gbytes of memory per core on the processor chip. Putting non-volatile memory on top of the logic chip will buy us twenty years of Moore's Law, said Williams.

Further out Williams said the memristor could be used for computation under a scheme called "implication logic" in a fraction of the area taken up in CMOS by Boolean logic. In addition a memristor device is a good analog of the synapse in brain function.

In conclusion Williams stressed that HP would not be getting into the semiconductor components business but would seek to commercialize and then license the technology to all comers

HP-Hynix-to-launch-memristor-memory-2013

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

HP moves to revolutionize computingquote:HP moves to revolutionize computing

HP has worked up quite a reputation for being the king of drama over the last several years. However, this week the company shifted the drama where it belongs: with the products.

Yes, HP announced an ARM based server platform targeted at Cloud applications that promises to significantly reduce server costs for companies like Amazon, Google, Facebook and other entities who live off of the web.

Genre classics resurrected as graphic novelsYet, this is just the beginning of a much bigger revolution.

In a session after the announcement, HP Labs talked about the new as the first step to replace processor architectures, networking, and storage as we know it with a fabric based on their unique Memristor technology which is apparently close to initial test fabrication.

This would suggest HP is actually on the cusp of a revolution similar to the transistor. If properly executed, the new paradigm could put the company at the heart of an intense technology storm.

The Problem with Current Architectures

Remember, whether we are talking PCs or servers, the base architecture goes back decades to before there was a web or high speed networks. Repositories were, back in the days of yore, measured in megabytes. Now they are gauged in terabytes, with bottlenecks moving from slow processors, to slow memory, latency and crawling networks. As such, most forms of storage and traditional copper networking has become increasingly inadequate and will likely hit a wall in a few short years.

Add these limitations to the cloud, the massive movement of data to the most optimized resource, and virtualization. What do you get? The potential for the mother of all performance killers - the current server and storage architecture.

Memristors + Tiny Cheap Cores

But what if you could break the storage, networking, and processor elements into tiny parts that could be reassigned and grouped in close proximity on demand?

Well, Memristors represent the best aspects of both magnetic media (they are non-volatile) and flash (they are fast to read and write, consume little power, and are solid state). So, what if you took these storage elements and put them in groups in close proximity, perhaps on the same boards, as ARM processors?

You’d then have ultrafast high-capacity storage in extreme proximity to power efficient cores. Meaning, half Memristor-powered racks would likely be equivalent to several racks of more traditional products. In addition, the close proximity, coupled with the high on-board speed and optical fiber connections between the boards, should result in not only a sharp performance increase but also facilitate massive power savings.

While the end products likely would initially look a lot like existing server blades or rack mounted servers, they could be built in almost any configuration; as while the circuit density is high, the thermal requirements are actually comparatively low. Since proximity will be the major problem - imagine servers that look more like balls or cubes than they do today at some future point to minimize the distance between components that may need to dynamically share loads.

In short, HP opened up a can of whoop-ass on the technology market and we really don’t see that very often.

Wrapping Up: Personal Technology?

Smartphones and tablets kicked off the trend toward very low cost cores and eventually, what appears to be an aggressively redesigned computing architecture. However, many of these changes can be applied to future generations of PCs, tablets and smartphones - providing ever higher performance at ever lower battery life.

Just try and think of future devices that will revolutionize the market by making current-gen iPads and iPhones look fat, slow, and power hungry. Of course, irrespective of whether or not this actually happens, the good news is that HP is back to providing product drama, something which is long overdue. The Meg Whitman HP is certainly looking better and better all the time.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:We report sub-nanosecond switching of a metal–oxide–metal memristor utilizing a broadband 20 GHz experimental setup developed to observe fast switching dynamics. Set and reset operations were successfully performed in the tantalum oxide memristor using pulses with durations of 105 and 120 ps, respectively. Reproducibility of the sub-nanosecond switching was also confirmed as the device switched over consecutive cycles.

iopsciencequote:In this work we demonstrated a platform for conducting

broadband dynamical studies of impedance mismatched

memristors. Tantalum oxide junctions were fabricated on

coplanar waveguide structures and reproducible resistance

switching of the order of 100 ps was shown. The measured

switching speed of this nonvolatile memory element is

comparable to or faster than mainstream volatile memories

such as DRAM and SRAM, and four orders of magnitude

faster than mainstream nonvolatile Flash. Additionally, the

result presented here opens new possibilities for the use of

memristors in high-speed high-frequency circuit applications.

......

The observed switching speed in this experiment was

limited by the pulse generator and not by the memristive device

itself nor by the transmission line structure. As a consequence,

one can envision that faster switching speeds in the double

digit picosecond range might be obtained by employing a faster

pulse generator as well as a compatible sample area in order to

minimize the parasitic effects associated with the memristor’s

parasitic capacitance.

Men heeft zelfs al ca 100 picoseconden schakeltijden gehaald met tantalium substraat memristor.

En het kan nog sneller want de testopstelling had erg veel last van parasitaire capaciteit en door die te reduceren zijn schakeltijden van enkele tientallen picoseconden haalbaar.

We hebben het dan over frequenties van ca 100 Ghz

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Klinkt interessant

This might be a surprise but it's true

That I'm not like you and I don't want your advice

Or your praise or to move in the ways you do

And I never will

That I'm not like you and I don't want your advice

Or your praise or to move in the ways you do

And I never will

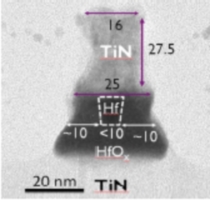

Bronquote:During IDEM, which is held in Washington, D.C. this week, the European research institute IMEC has shown the first 10nm RRAM cell. RRAM is often also referred to as a memristor.

The area of the cell is 100nm² and is based on hafnium/hafnium-oxide as the switching material. This material is placed between conventional contacts in a cross bar array. The contacts are made of titanium-nitride.

Cross section of IMEC 10nm RRAM cell. Copyright IMEC.

The cell has demonstrated an endurance of more than 1 billion reads/writes and switches in about 1ns. IMEC has extrapolated the data retention period to 10 years at 100 degrees C. Excellent life-span next to a hot GPU.

If manufacturing hurdles can be overcome, then this cell clearly demonstrates that RRAM will be superior to both NAND flash as well as conventional DRAM.

In order to use its potential fully then programmers will start to think of different ways to write programs since memory and storage over time could merge to one large linear space.

Hafnium als memristor-substraat is dus ook geschikt. Hafnium wordt sinds kort gebruikt als HKMG omdat hafnium-oxide een betere isolator is dan het gebruikelijke silicium-oxide. Bij de nanostucturen die men nu gebruikt kan men daarmee de aanzienlijke lekstromen reduceren. De halfgeleider industrie is dus als bekent met het toepassen van Hafnium in IC´s. Dit maakt een snelle lab to market introductie mogelijk zoals ook met het titanium wat HP gebruikt in hun memristors. Hafnium is echter veel kostbaarder dan titanium.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Cool! Ik heb memristors altijd al interessant gevonden ivm de "continue" opslag eigenschap die erg lijkt op die van een synaps in de menselijke hersens. (Natuurlijk is dit maar een klein klein onderdeel van de mechanismen daar..)quote:Op donderdag 15 december 2011 23:07 schreef Digi2 het volgende:

[..]

Bron

[ afbeelding ]

Hafnium als memristor-substraat is dus ook geschikt. Hafnium wordt sinds kort gebruikt als HKMG omdat hafnium-oxide een betere isolator is dan het gebruikelijke silicium-oxide. Bij de nanostucturen die men nu gebruikt kan men daarmee de aanzienlijke lekstromen reduceren. De halfgeleider industrie is dus als bekent met het toepassen van Hafnium in IC´s. Dit maakt een snelle lab to market introductie mogelijk zoals ook met het titanium wat HP gebruikt in hun memristors. Hafnium is echter veel kostbaarder dan titanium.

Bronquote:Elpida Announces 64Mb ReRAM, Sees 8Gb Product in 2013

Jan 26, 2012 12:03 Jyunichi Oshita, Nikkei Electronics

Elpida Memory had a press conference Jan 24, 2012, and Takao Adachi, who is responsible for the development of the new memory, explained about the latest technology.

The new ReRAM. Each of its four areas is a 64-Mbit memory array.

Elpida Memory Inc developed ReRAM (resistive random-access memory), which is expected to be one of the next-generation nonvolatile memories.

The company prototyped the ReRAM by using 50nm process technology to form 64-Mbit cell arrays and confirmed operation of all bits. It has already started making efforts towards commercialization of the ReRAM.

"We want to launch an 8-Gbit product made by using 30nm process technology (as the first product) in 2013," said Takao Adachi, director of Elpida. "We will be ready for full-scale volume production in 2014."

Elpida plans to target the ReRAM at mobile machines such as smartphones, tablet computers and notebook computers. It expects that the ReRAM will be used as cache memory to fill a performance gap between DRAM and NAND flash memory in those machines.

"We hope that it will eventually be a memory that can replace DRAM because mobile machine makers want to reduce the amount of DRAM (which consumes a large amount of power) as much as possible and replace it with nonvolatile memory," Adachi said.

At this point, however, many of its customers that develop video-related stationary machines and want to enhance the speed of SSD are showing interest in the ReRAM, he said.

The new ReRAM is a 1T-1R-type ReRAM developed by using variable resistance elements based on hafnium (Hf) oxide. Its data reading speed is 20ns or faster, and it can be rewritten one million times or more. Elpida plans to completely clarify the mechanism of its operation and reduce the variation in the operation of memory elements in the aim of increasing its capacity to higher than 1 Gbit.

Though the ReRAM was prototyped by using 6F2 cells this time, Elpida intends to use 4F2 cells for volume production of the memory and reduce cell area. It can be mass-produced in production lines for DRAMs. For volume production, the company aims to achieve a bit cost 30% lower than that of DRAM.

Elpida has already decided to develop only ReRAM as its next-generation nonvolatile memory and is not developing MRAM (magnetic random access memory) or PRAM (phase-change random access memory).

The ReRAM was developed in collaboration with Sharp Corp, Japan's National Institute of Advanced Industrial Science and Technology (AIST) and the University of Tokyo in a project sponsored by New Energy and Industrial Technology Development Organization (NEDO) (See related article). The project was launched in 2010.

Tweakers

Dus na HP komt nu ook Elpida 2013/2014 met commercieel memristor geheugen op de markt.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

quote:Op donderdag 2 september 2010 00:49 schreef Maanvis het volgende:

wow, als dit er komt dan kan ik toch zeggen tegen mijn vrienden dat ik erbij was toen het bedacht werd op FOK!

quote:Panasonic and TSMC Tip Resistive RAMs at ISSCC

Foundry looking for embedded memory solution

-----------------------

By Mark LaPedus, SemiMD senior editor

The emerging resistive RAM (ReRAM) market continues to heat up, as Panasonic and Taiwan Semiconductor Manufacturing Co. Ltd. (TSMC) will describe new breakthroughs in the arena.

At the International Solid-State Circuits Conference (ISSCC) in San Francisco on Wednesday (Feb. 22), TSMC will describe a ReRAM as part of the silicon foundry’s push in the embedded memory space. TSMC, along with National Tsing Hua University in Hsinchu, Taiwan, will disclose the development of a 0.5-Volt, 4-Mbit embedded ReRAM macro, based on a 65nm logic process.

At ISSCC, Panasonic will describe an 8-Mbit multi-layered cross-point ReRAM macro. The device has a 443-MB/second write throughput at 8.2nm pulse widths, which is twice as fast as competing efforts, according to Panasonic. Read access time is said to be 25ns.

Last year, Panasonic claimed to be sampling a 2-Mbit ReRAM, based on a tantalum and oxygen (TaOx) process. The 8-Mbit ReRAM uses the same technology, reportedly based on a 0.18-micron process.

Panasonic's ReRAM structure (Source: Company)

The ISSCC announcements follow what could be the hottest technology within the next-generation memory space. Elpida, Hynix, IMEC, Micron, Samsung, Sharp, Sony and others are working on ReRAM. ReRAM is “based on the electronic switching of a resistor element material between two stable (low/high) resistive states. The major strengths of ReRAM technology are its potential density and speed,” according to IMEC.

FRAM, MRAM, phase-change, ReRAM and others fall into the so-called universal memory category. Developers of these technologies claim their respective technologies can replace DRAM, NAND and NOR — or all three.

Most next-generation memory types have failed to live up to their promises. They are difficult to make and scale. But some claim the floating gate structure in flash is expected to hit the wall at 14nm, thereby fueling the need for a new memory type.

There are a range of emerging applications for next-generation memories. One of the possibilities is so-called storage-class memories. In this application, there is a need for a new and faster memory that sits between the processor and DRAM in a system to boost I/O performance. In theory, a storage-class memory would offload many of the functions in a power-hungry DRAM.

Block diagram of ReRAM from National Tsing Hua University and TSMC (Source: TSMC, National Tsing)

Embedded is another application. Many foundries offer embedded DRAM IP for system LSIs and other applications, but the technology could soon hit the scaling wall.

In embedded applications, “MRAM and ReRAM have the most promise,” said Fu-Lung Hsueh, a TSMC fellow and director of the Design Technology Division for the foundry giant, in a brief interview at ISSCC.

For some time, TSMC and Qualcomm Inc. have been developing an embedded memory based on MRAM technology. In the future, Qualcomm hopes to incorporate the MRAM IP within its cell-phone chip offerings.

ReRAM is another possibility for the embedded market. TSMC and National Tsing Hua University are developing a ReRAM solution. Hsueh said the device is still in the “prototyping” stage and the work is being conducted at the university level.

That device is said to enable short write times at low voltages. The 4-Mbit macro has four 1-Mbit sub-arrays, comprising of 2,048 columns and 512 rows, according to a paper from TSMC and National Tsing Hua. The entities developed a body-drain-driven current-mode sense amplifier (CSA) and small voltage headroom (VHR) for larger sensing margins. Using a new sensing scheme, the device is said to have a 45ns random read time, according to the paper.

chipdesignmagazine

zdnetquote:Ook Sandisk zet in op SSD-killer ReRAM

Geheugen van de toekomst

22 februari 2012 | Jan Custers

ZDNet.nl

Flashgeheugenfabrikant Sandisk zet een team van specialisten op de ontwikkeling van ReRAM-geheugen. Dat zou zowel het hedendaagse werk- als opslaggeheugen kunnen vervangen.

Sandisk plaatste vorige week een vacature op zijn website voor een verantwoordelijke van een dertigkoppig onderzoeksteam dat de productie van op memristors gebaseerd resistief RAM-geheugen (ReRAM) mogelijk moet maken. Het doet dat in samenwerking met partner Toshiba. Dat merkte Bright Side of News op.

Technologie evolueert snel

Vorige maand beweerde de Japanse geheugenfabrikant Elpida dat het samen met elektronicagigant Sharp een prototype van ReRAM-geheugen had ontwikkeld met dezelfde lees- en schrijfsnelheden als het DRAM-geheugen in hedendaagse computers.

Ook Panasonic, Sony, Micron, DSI en HP - in samenwerking met Hynix Seminconductor – investeren in de technologie. Die steunt op de revolutionaire ‘memristor’ die HP in 2008 ontwikkelde. Het eerste commerciële ReRAM-product wordt rond 2013 verwacht.

Snel en niet-vluchtig

ReRAM wordt naar voren geschoven als de opvolger van zowel het huidige systeem- als opslaggeheugen in computers. De technologie combineert de lees- en schrijfsnelheid van DRAM-geheugen met de niet-vluchtige aard van flashgeheugen. Dat betekent dat gegevens bewaard blijven als de spanning wegvalt. In theorie zal een computer met genoeg ReRAM-geheugen geen laadtijden meer kennen.

Jammer genoeg ligt Elpida ff uit de race, het bedrijf heeft faillisement moeten aanvragen.

De ex CEO van Sandisk denkt ook dat de memristor de nieuwe generatie geheugen gaat worden.

De kaarten lijken geschut, alle grote geheugenfabrikanten zijn nu met reram in de weer met aanzienlijke teams. Voor flashgeheugen liggen er aanzienlijke obstakels bij verdere structuurverkleining. De energie en gelden die trachten te overkomen ziet men blijkbaar beter besteed in een nieuw type geheugen met nog legio mogelijkheden tot structuurverkleining, substraat optimalisaties en 3D implementatie.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

De opvolgers van Reram tekenen zich trouwens ook al af.

1. Moleculair geheugen.

Slechts 1 molecuul wordt gebruikt als schakelaar. IBM en HP doen hier veel onderzoek naar.

Dit geheugen kent geen ¨slijtage/material deformation¨ zoals flash en memristor geheugen.

Het is een eenvoudige spin-off van Oled technologie, een opkomende miljardenmarkt.

2. Quantum geheugen. Ook hier heeft IBM enige doorbraken gemaakt. Dit lijkt op Dram in de zin dat er ¨gerefreshed¨ moet worden vanwege decoherentie. Door het koppelen van enkele qubits is echter een schier oneindig geheugen in bits/bytes te defineren.

Bepaalde vraagstukken laten zich met quantumcomputers oplossen die voor klassieke digitale computers zeer moeilijk zoniet onmogelijk zijn.

1. Moleculair geheugen.

Slechts 1 molecuul wordt gebruikt als schakelaar. IBM en HP doen hier veel onderzoek naar.

Dit geheugen kent geen ¨slijtage/material deformation¨ zoals flash en memristor geheugen.

Het is een eenvoudige spin-off van Oled technologie, een opkomende miljardenmarkt.

2. Quantum geheugen. Ook hier heeft IBM enige doorbraken gemaakt. Dit lijkt op Dram in de zin dat er ¨gerefreshed¨ moet worden vanwege decoherentie. Door het koppelen van enkele qubits is echter een schier oneindig geheugen in bits/bytes te defineren.

Bepaalde vraagstukken laten zich met quantumcomputers oplossen die voor klassieke digitale computers zeer moeilijk zoniet onmogelijk zijn.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Gizmoquote:Samsung realizes ReRAM's rewritability of one trillion times

Resistive Random Access Memory (ReRAM) technology has been making the news rounds throughout the electronic market since its inception back in 1997. Panasonic had led the way for commercial mass production as this next generation iteration of non-volatile memory types is being developed by a multitude of companies. But this time, Samsung has rather notched a level by contriving a performance enhancing technology, which boosts the ReRAM's rewritability capacity to a mind-boggling 1 trillion times!

Fundamentally, this new advanced technology utilizes asymmetric Ta2O5-x/TaO2-x bi-layer laminated film as the resistivity-varying material, instead of the conventional Ta2O5 film. The new material contributes to localized resistance switching. The reduction in switching current in turn allows for lesser power consumption, along with extreme cycling endurance of over 1 trillion.

The figures speak for themselves as this touted one trillion mark capability is about one million times more than that of the latest flash memory. Moreover, with switching times of only 10ns, the fascinating technology can be applied in cases of working-memory space.

Geld maakt meer kapot dan je lief is.

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het zijn sterke ruggen die vrijheid en weelde kunnen dragen

Het is een combinatie van geheugen en weerstandquote:Op donderdag 29 maart 2012 18:49 schreef Senor__Chang het volgende:

Kan iemand dit uitleggen voor de leek?

Trots lid van het 👿 Duivelse Viertal 👿

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Een gedicht over Maanvis

Het ONZ / [KAMT] Kennis- en Adviescentrum Maanvis Topics , voor al je vragen over mijn topiques!

Dus computers worden nog sneller ofzo? En wat zouden we dan met die extra snelheid kunnen doen dat zo revolutionair is?

Als ik het goed heb begrepen is het lijstje voordelen van zo'n component (als het doorontwikkeld wordt):quote:Op vrijdag 30 maart 2012 01:30 schreef Senor__Chang het volgende:

Dus computers worden nog sneller ofzo? En wat zouden we dan met die extra snelheid kunnen doen dat zo revolutionair is?

- Minder energieverbruik om data te schrijven/lezen

- Sneller data wegschrijven

- Minder defect-gevoelig (want minder losse componenten)

- Meer data per vierkante cm. Altijd fijn.

Health In Harmony is een non-profitorganisatie die regenwoudgemeenschappen helpt met gezondheidszorg en duurzame inkomens in ruil voor bosbescherming, en zo tegelijk klimaatverandering en armoede aanpakt. - https://www.healthinharmony.org/

Ik ga uit van sarcasme maar toch nog even dit.quote:Op vrijdag 30 maart 2012 01:42 schreef Senor__Chang het volgende:

Oh ok, maar niks revolutionairs dus?

Elk technologische paradigma heeft een bepaalde levensduur totdat iets zo ver uitontwikkeld is dat er geen rek meer in zit. Electronenbuizen werden vervangen door transistors die de jaren daarop ook weer kleiner en kleiner werden. Transistors liepen ook weer tegen limieten aan qua productiesnelheid en toen gingen we allemaal over op integrated circuits.

Paradigmaverschuivingen zijn een essentieel onderdeel van de gemiddelde 35% per jaar kosten afname, snelheid/capaciteitstoename. Dat fenomeen heet ook wel Moore's Law

Besef even dat de verticale schaal logaritmisch is.

Health In Harmony is een non-profitorganisatie die regenwoudgemeenschappen helpt met gezondheidszorg en duurzame inkomens in ruil voor bosbescherming, en zo tegelijk klimaatverandering en armoede aanpakt. - https://www.healthinharmony.org/

|

|